作者(zhě):魚丸粗(cū)面(miàn)

本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

在(zài)上(shàng)一(yī)篇(piān)的(de)文(wén)章(zhāng)《1.LATTICE DIAMOND的(de)LICENSE申請方(fāng)法》中(zhōng),我(wǒ)为(wèi)大家(jiā)詳细(xì)介紹了(le)Lattice開(kāi)發(fà)工具Diamond的(de)安(ān)裝(zhuāng)以(yǐ)及(jí)license生(shēng)成(chéng)方(fāng)法。Diamond開(kāi)發(fà)工具下(xià)载鍊(liàn)接在(zài)明(míng)德揚的(de)官方(fāng)論壇上(shàng)已經(jīng)更(gèng)新,有(yǒu)需要(yào)的(de)同(tóng)学請到(dào)官方(fāng)論壇自(zì)取(qǔ)。Diamond 3.10開(kāi)發(fà)工具下(xià)载傳送門(mén):

http://www.fpgabbs.cn/forum.php?mod=forumdisplay&fid=58。

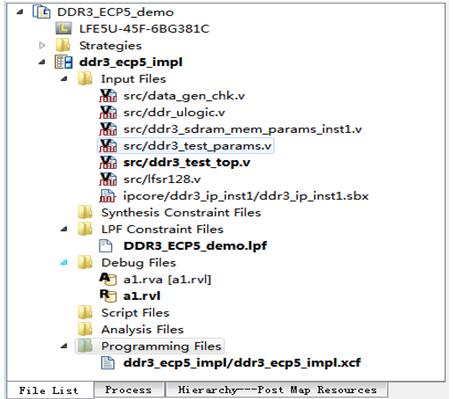

首先(xiān)了(le)解(jiě)一(yī)下(xià)软(ruǎn)件(jiàn)界面(miàn)。工程生(shēng)成(chéng)後(hòu),会(huì)在(zài)File List狀态欄中(zhōng)顯示工程的(de)芯片(piàn)型号(hào)、工程文(wén)件(jiàn)、管(guǎn)脚配置文(wén)件(jiàn)、調試文(wén)件(jiàn)、以(yǐ)及(jí)編譯後(hòu)的(de)文(wén)件(jiàn)等信(xìn)息(如(rú)下(xià)图(tú)1):

图(tú)1 File List界面(miàn)信(xìn)息

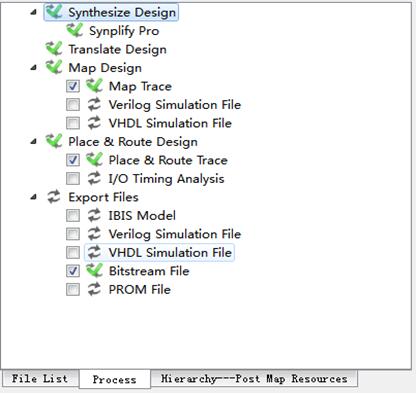

Process狀态欄顯示的(de)是(shì)工程的(de)綜合、生(shēng)成(chéng)下(xià)载文(wén)件(jiàn)过(guò)程,其中(zhōng)包(bāo)括工程的(de)綜合、布(bù)局(jú)布(bù)線(xiàn),和(hé)待燒录(lù)文(wén)件(jiàn)的(de)生(shēng)成(chéng)(如(rú)下(xià)图(tú)2)。Hierarchy狀态欄可(kě)以(yǐ)用(yòng)来(lái)查看(kàn)添加的(de)IP核有(yǒu)沒(méi)有(yǒu)編譯進(jìn)工程中(zhōng)。

图(tú)2 Process界面(miàn)信(xìn)息

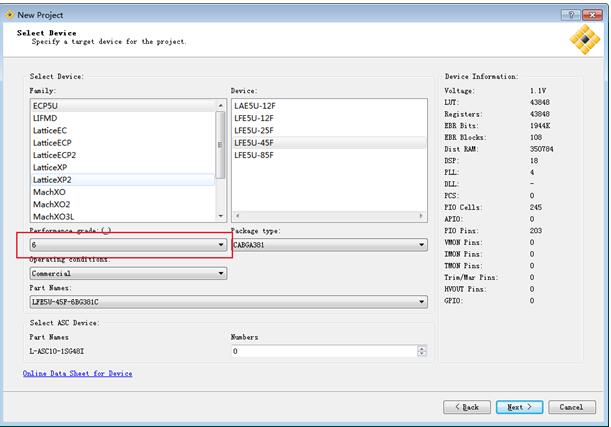

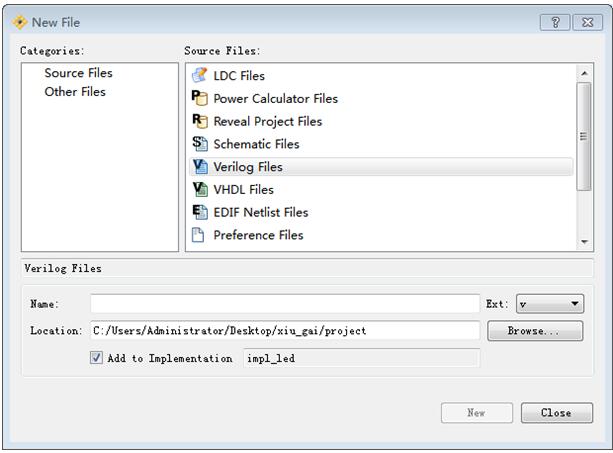

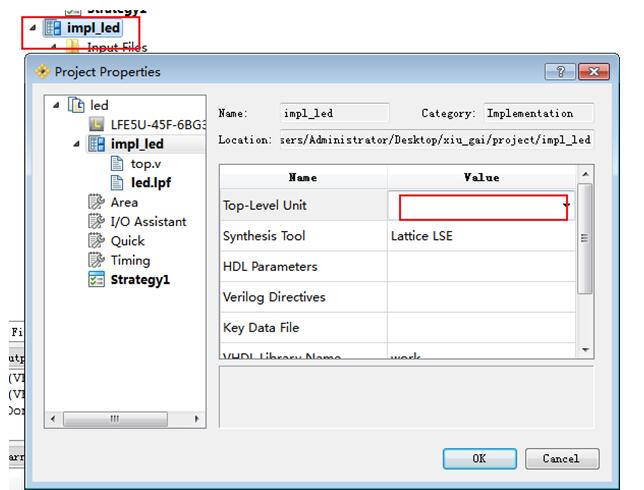

下(xià)面(miàn)来(lái)新建一(yī)个(gè)工程。Diamond建立工程的(de)过(guò)程與(yǔ)Quartus類(lèi)似,點(diǎn)擊File→New→Project来(lái)打(dǎ)開(kāi)工程建立窗(chuāng)口(kǒu)。在(zài)Project Name界面(miàn)中(zhōng)分(fēn)别为(wèi)工程和(hé)綜合後(hòu)的(de)文(wén)件(jiàn)命名以(yǐ)及(jí)選擇保存的(de)文(wén)件(jiàn)位置;在(zài)Select Device界面(miàn)对(duì)FPGA芯片(piàn)進(jìn)行選擇,在(zài)要(yào)編程的(de)FPGA芯片(piàn)系(xì)列下(xià)找(zhǎo)到(dào)对(duì)應(yìng)的(de)型号(hào),这(zhè)里(lǐ)需要(yào)注意(yì)的(de)是(shì)芯片(piàn)的(de)速度(dù)等級要(yào)與(yǔ)实際的(de)芯片(piàn)型号(hào)对(duì)應(yìng)上(shàng),否則燒录(lù)的(de)时(shí)候会(huì)出(chū)現(xiàn)錯誤(如(rú)下(xià)图(tú)3)。Select Synthesis Tool界面(miàn)選擇編譯工具,这(zhè)里(lǐ)選擇Diamond自(zì)带(dài)的(de)編譯工具Lattice LSE,也(yě)可(kě)以(yǐ)選擇外(wài)部(bù)編譯工具Synplify Pro。工程生(shēng)成(chéng)之後(hòu),会(huì)在(zài)File List界面(miàn)顯示工程的(de)芯片(piàn)信(xìn)息、工程文(wén)件(jiàn)等。工程建立後(hòu),需要(yào)添加文(wén)件(jiàn),右(yòu)鍵點(diǎn)擊Input Files→Add→New File,在(zài)弹出(chū)的(de)窗(chuāng)口(kǒu)中(zhōng)選擇Verilog Files(或(huò)VHDL Files),選擇好(hǎo)文(wén)件(jiàn)目录(lù)和(hé)文(wén)件(jiàn)名,即可(kě)添加一(yī)个(gè)空白的(de)文(wén)件(jiàn)(如(rú)下(xià)图(tú)4)。設計(jì)好(hǎo)各(gè)个(gè)模块(kuài)後(hòu),需要(yào)指定(dìng)一(yī)个(gè)頂层文(wén)件(jiàn),右(yòu)鍵點(diǎn)擊Impl_xx(如(rú)下(xià)图(tú)5),在(zài)弹出(chū)的(de)界面(miàn)中(zhōng)找(zhǎo)到(dào)Top-Level Unit,在(zài)右(yòu)側空白欄中(zhōng)輸入(rù)需要(yào)設置为(wèi)頂层模块(kuài)的(de)名稱即可(kě)。

图(tú)3 芯片(piàn)選型界面(miàn)

图(tú)4 添加V文(wén)件(jiàn)

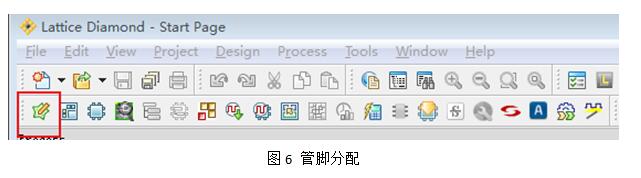

工程文(wén)件(jiàn)建立好(hǎo)後(hòu),需要(yào)編譯一(yī)下(xià),在(zài)第(dì)二(èr)欄Process中(zhōng)双(shuāng)擊Synthesis Design对(duì)工程進(jìn)行編譯。編譯通(tòng)过(guò)後(hòu)需要(yào)分(fēn)配管(guǎn)脚,找(zhǎo)到(dào)界面(miàn)上(shàng)方(fāng)工具欄第(dì)三(sān)行最(zuì)左(zuǒ)側图(tú)标(biāo)SpreadSheet View(如(rú)下(xià)图(tú)6)進(jìn)行管(guǎn)脚分(fēn)配。管(guǎn)脚分(fēn)配完成(chéng)後(hòu)在(zài)Process狀态欄中(zhōng)勾選Map Design下(xià)的(de)Map Trace和(hé)Place & Route Design下(xià)的(de)Place & Route Trace,双(shuāng)擊Place & Route Design進(jìn)行布(bù)局(jú)布(bù)線(xiàn),通(tòng)过(guò)以(yǐ)後(hòu)勾選Export Files下(xià)的(de)Bitstream File并双(shuāng)擊Export Files生(shēng)成(chéng)BIT流文(wén)件(jiàn)。

到(dào)这(zhè)里(lǐ),一(yī)个(gè)工程的(de)bit流文(wén)件(jiàn)已生(shēng)成(chéng)成(chéng)功,在(zài)接下(xià)来(lái)的(de)文(wén)章(zhāng)中(zhōng),我(wǒ)会(huì)繼續向(xiàng)大家(jiā)介紹bit流文(wén)件(jiàn)的(de)燒录(lù)以(yǐ)及(jí)工程IP核的(de)添加、在(zài)線(xiàn)調試工具Reveal的(de)使用(yòng),希望大家(jiā)可(kě)以(yǐ)有(yǒu)所(suǒ)收(shōu)獲。