明(míng)德揚在(zài)PCIE高(gāo)速傳輸方(fāng)案(àn)積累了(le)豐富的(de)技術(shù),傳輸的(de)带(dài)宽(kuān)利用(yòng)率可(kě)达(dá)到(dào)90%以(yǐ)上(shàng),延遲可(kě)达(dá)到(dào)理論的(de)最(zuì)低延遲值。

明(míng)德揚能(néng)够根(gēn)據(jù)客戶的(de)需求(需求、延遲和(hé)應(yìng)用(yòng)等),为(wèi)客戶提(tí)供定(dìng)制的(de)PCIE解(jiě)決方(fāng)案(àn),欢迎您與(yǔ)我(wǒ)们(men)聯系(xì),沟(gōu)通(tòng)洽談。

下(xià)面(miàn)是(shì)我(wǒ)司为(wèi)客戶定(dìng)制的(de)方(fāng)案(àn)介紹,該方(fāng)案(àn)已經(jīng)應(yìng)用(yòng)到(dào)航天(tiān)航空、雷(léi)达(dá)等領域,經(jīng)受住客戶和(hé)市(shì)场的(de)檢验(yàn)。

一(yī)、 高(gāo)效率傳輸方(fāng)案(àn)

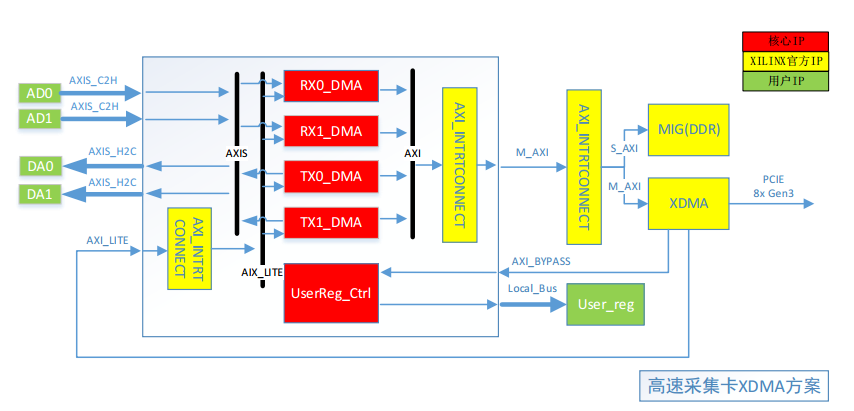

該采集方(fāng)案(àn) Demo 基于(yú) VC709 開(kāi)發(fà)板,使用(yòng) XILINX 官方(fāng) XDMA IP 核配合板载高(gāo)速 DDR3,可(kě)对(duì)前(qián)端 ADC 産生(shēng)的(de)不(bù)大于(yú) 4.5GB/s 的(de)連(lián)續或(huò)非(fēi)連(lián)續數據(jù)進(jìn)行实时(shí)采集,同(tóng)时(shí)該采集卡(kǎ)具備數據(jù)發(fà)送功能(néng),可(kě)以(yǐ)将用(yòng)戶文(wén)件(jiàn)或(huò)者(zhě)內(nèi)存中(zhōng)的(de)數據(jù)写到(dào) FPGA 的(de)發(fà)送 FIFO 中(zhōng),速率約为(wèi)4.5GB/s,該采集卡(kǎ)具備上(shàng)位機(jī)读(dú)写 FPGA 用(yòng)戶寄存器的(de)功能(néng),读(dú)写接口(kǒu)为(wèi) local bus 接口(kǒu),方(fāng)便易用(yòng)。

1. 系(xì)統結構图(tú)

方(fāng)案(àn)一(yī)

2. 采用(yòng)此(cǐ)方(fāng)案(àn)的(de)某項目性(xìng)能(néng)

1) 支持(chí) 4 通(tòng)道(dào) AD 數據(jù)同(tóng)时(shí)上(shàng)行,支持(chí) 4 通(tòng)道(dào) DA 數據(jù)同(tóng)时(shí)下(xià)行;

2) PCIE 鍊(liàn)路(lù)为(wèi) 8x Gen3 时(shí), 數據(jù)傳輸带(dài)宽(kuān)大于(yú) 4GB/s,誤碼率低于(yú) 10-14;

3) 使用(yòng)最(zuì)新 XILINX 官方(fāng) XDMA 驅動(dòng),稳定(dìng)可(kě)靠;

4) 支持(chí) 16 路(lù)用(yòng)戶中(zhōng)斷;

5) 支持(chí) XILINX 7 系(xì)列以(yǐ)上(shàng)的(de)全(quán)系(xì) FPGA;

6) 5.支持(chí) Windows/Linux 系(xì)統;

二(èr)、 低延遲采集方(fāng)案(àn)

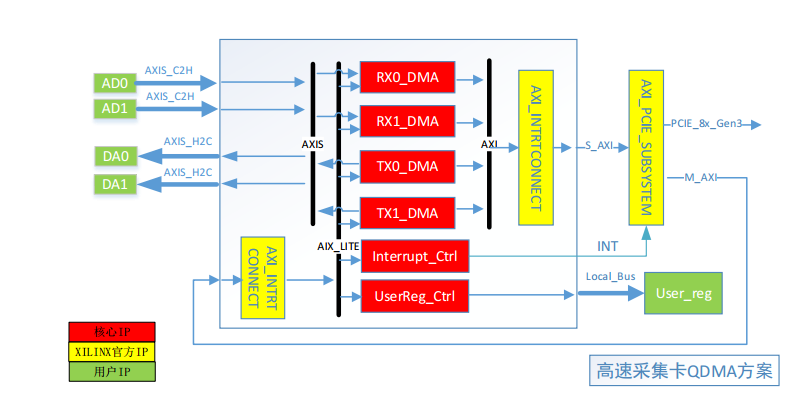

該采集方(fāng)案(àn) Demo 基于(yú) KU115 開(kāi)發(fà)板,使用(yòng)自(zì)研 QDMA IP 核,无需板载 DDR, 可(kě)对(duì)前(qián)端ADC 産生(shēng)的(de)不(bù)大于(yú) 6GB/s 的(de)連(lián)續或(huò)非(fēi)連(lián)續數據(jù)進(jìn)行实时(shí)采集,同(tóng)时(shí)該采集卡(kǎ)具備數據(jù)發(fà)送功能(néng),可(kě)以(yǐ)将用(yòng)戶文(wén)件(jiàn)或(huò)者(zhě)內(nèi)存中(zhōng)的(de)數據(jù)写到(dào) FPGA 的(de)發(fà)送 FIFO 中(zhōng),速率約为(wèi) 5.5GB/s,該采集卡(kǎ)具備上(shàng)位機(jī)读(dú)写 FPGA 用(yòng)戶寄存器的(de)功能(néng),读(dú)写接口(kǒu)为(wèi) local bus 接口(kǒu),方(fāng)便易用(yòng)。

1. 結構框图(tú)

方(fāng)案(àn)二(èr)

2. 采用(yòng)此(cǐ)方(fāng)案(àn)的(de)某項目性(xìng)能(néng)

1) 最(zuì)高(gāo)支持(chí) 8 通(tòng)道(dào) AD 數據(jù)同(tóng)时(shí)上(shàng)行,最(zuì)高(gāo)支持(chí) 8 通(tòng)道(dào) DA 數據(jù)同(tóng)时(shí)下(xià)行;

2) PCIE 鍊(liàn)路(lù)为(wèi) 8x Gen3 时(shí),數據(jù)傳輸带(dài)宽(kuān)大于(yú) 5.7GB/s,誤碼率低于(yú) 10-14;

3) 驅動(dòng)采用(yòng)類(lèi) DPDK 架構,通(tòng)过(guò)轮詢模式, 內(nèi)存零(líng)拷貝機(jī)制,可(kě)达(dá)到(dào)理論最(zuì)低延遲。

4) 支持(chí) 16 路(lù)用(yòng)戶中(zhōng)斷;

5) 支持(chí) XILINX 7 系(xì)列以(yǐ)上(shàng)的(de)全(quán)系(xì) FPGA;

6) 支持(chí) Windows/Linux 系(xì)統;

三(sān)、 方(fāng)案(àn)價格

真(zhēn)实的(de)價格取(qǔ)決于(yú)方(fāng)案(àn)的(de)技術(shù)指标(biāo)、項目周期(qī)等因(yīn)素,欢迎洽談了(le)解(jiě)。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 前(qián)端模拟采集、射頻、電(diàn)荷靈敏前(qián)置放(fàng)大器

明(míng)德揚科技教育

明(míng)德揚科技教育