利用(yòng)FPGA实現(xiàn)外(wài)設通(tòng)信(xìn)接口(kǒu)之: 典型实例-字(zì)符LCD接口(kǒu)的(de)設計(jì)與(yǔ)实現(xiàn)

实例的(de)內(nèi)容及(jí)目标(biāo)

1.实例的(de)主(zhǔ)要(yào)內(nèi)容

本(běn)节(jié)旨在(zài)設計(jì)实現(xiàn)FPGA與(yǔ)字(zì)符LCD的(de)接口(kǒu),幫助读(dú)者(zhě)進(jìn)一(yī)步了(le)解(jiě)字(zì)符液晶的(de)工作原理和(hé)設計(jì)方(fāng)法。

2.实例目标(biāo)

通(tòng)过(guò)本(běn)实例,读(dú)者(zhě)應(yìng)达(dá)到(dào)以(yǐ)下(xià)目标(biāo)。

· 学習字(zì)符型液晶顯示器的(de)控制原理。

· 掌握利用(yòng)FPGA設計(jì)驅動(dòng)的(de)基本(běn)思(sī)想(xiǎng)和(hé)方(fāng)法。

· 熟練掌握狀态機(jī)的(de)使用(yòng)。

字(zì)符LCD接口(kǒu)实例內(nèi)容

紅(hóng)色(sè)飓风開(kāi)發(fà)板配套(tào)的(de)字(zì)符液晶模块(kuài)为(wèi)2行,每行16个(gè)字(zì)符。本(běn)实要(yào)求顯示功能(néng)如(rú)下(xià):第(dì)一(yī)行顯示“Welcome RedLogic World !”,第(dì)二(èr)行顯示“RedLogic World!”,由(yóu)于(yú)一(yī)行只(zhī)能(néng)顯示16个(gè)字(zì)符,因(yīn)此(cǐ)要(yào)整屏左(zuǒ)移顯示。

FPGA代(dài)碼設計(jì)实現(xiàn)

本(běn)設計(jì)的(de)程序主(zhǔ)要(yào)包(bāo)含两(liǎng)个(gè)模块(kuài),一(yī)个(gè)模块(kuài)为(wèi)char_ram,另(lìng)一(yī)个(gè)模块(kuài)为(wèi)LCD的(de)驅動(dòng)模块(kuài)lcd。

char_ram模块(kuài)的(de)主(zhǔ)要(yào)功能(néng)是(shì)根(gēn)據(jù)輸入(rù)的(de)地(dì)址,輸出(chū)相應(yìng)字(zì)符在(zài)CGRM(字(zì)符存儲發(fà)生(shēng)器)中(zhōng)的(de)地(dì)址。因(yīn)为(wèi)在(zài)控制LCD顯示时(shí),只(zhī)需用(yòng)戶提(tí)供相應(yìng)字(zì)符的(de)地(dì)址,就(jiù)可(kě)以(yǐ)顯示出(chū)該字(zì)符。

在(zài)char_ram中(zhōng),先(xiān)設置好(hǎo)所(suǒ)有(yǒu)字(zì)符对(duì)應(yìng)的(de)地(dì)址,然後(hòu)給(gěi)需要(yào)用(yòng)到(dào)的(de)字(zì)符定(dìng)義新的(de)地(dì)址用(yòng)于(yú)選擇輸出(chū)。

Lcd模块(kuài)用(yòng)于(yú)驅動(dòng)lCD正(zhèng)常工作。LCD是(shì)一(yī)个(gè)慢(màn)顯示器件(jiàn),因(yīn)此(cǐ)时(shí)鐘(zhōng)一(yī)定(dìng)要(yào)滿足要(yào)求,在(zài)这(zhè)里(lǐ)通(tòng)过(guò)50MHz分(fēn)頻得到(dào)輸入(rù)的(de)时(shí)鐘(zhōng)周期(qī)約为(wèi)100µs(約10Hz),以(yǐ)滿足慢(màn)顯要(yào)求。LCD的(de)驅動(dòng)模块(kuài)利用(yòng)一(yī)个(gè)狀态機(jī)来(lái)实現(xiàn)。具體(tǐ)程序參考实例源代(dài)碼。

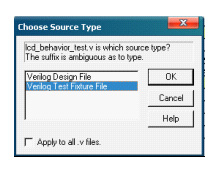

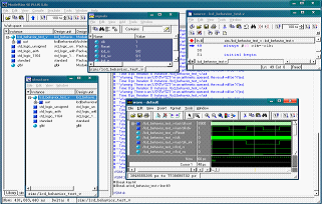

ModelSim仿真(zhēn)验(yàn)證

通(tòng)过(guò)Add Source的(de)方(fāng)法直(zhí)接将测試代(dài)碼加入(rù)到(dào)工程當中(zhōng)。選中(zhōng)要(yào)加入(rù)的(de)测試代(dài)碼文(wén)件(jiàn):led_behavor_test.v,弹出(chū)如(rú)图(tú)10.37所(suǒ)示的(de)对(duì)話(huà)框,選擇“Verilog Text Fixture File”。

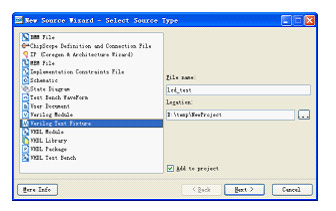

用(yòng)戶也(yě)可(kě)以(yǐ)直(zhí)接新建一(yī)个(gè)仿真(zhēn)文(wén)件(jiàn),選擇“New Source”,選擇“Verilog Test Fixture”,輸入(rù)测試文(wén)件(jiàn)名稱,如(rú)图(tú)10.38所(suǒ)示,單擊“Next”按鈕。

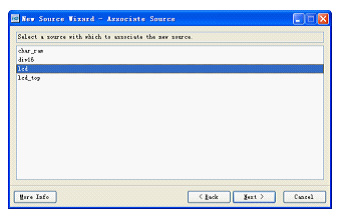

選擇lcd模块(kuài)(对(duì)哪个(gè)模块(kuài)進(jìn)行测試,就(jiù)選擇哪个(gè)文(wén)件(jiàn)),如(rú)下(xià)图(tú)所(suǒ)示。

選擇源文(wén)件(jiàn)類(lèi)型

新建仿真(zhēn)源文(wén)件(jiàn)

選擇被(bèi)测試模块(kuài)

新建测試文(wén)件(jiàn)後(hòu),ISE会(huì)自(zì)動(dòng)生(shēng)成(chéng)一(yī)部(bù)分(fēn)代(dài)碼,其餘內(nèi)容可(kě)直(zhí)接從源工程中(zhōng)提(tí)供的(de)测試文(wén)件(jiàn)中(zhōng)複制。

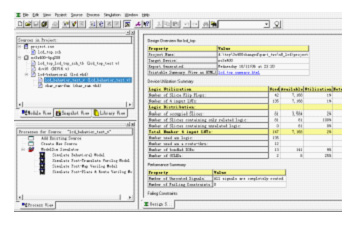

添加後(hòu)選中(zhōng)测試文(wén)件(jiàn)可(kě)以(yǐ)看(kàn)到(dào)如(rú)下(xià)图(tú)所(suǒ)示

仿真(zhēn)文(wén)件(jiàn)信(xìn)息

在(zài)Process for source下(xià)有(yǒu)4个(gè)M的(de)图(tú)标(biāo),分(fēn)别对(duì)應(yìng)4个(gè)級别的(de)仿真(zhēn)。從上(shàng)至(zhì)下(xià),第(dì)一(yī)个(gè)为(wèi)行为(wèi)仿真(zhēn),第(dì)二(èr)个(gè)为(wèi)翻譯後(hòu)仿真(zhēn),第(dì)三(sān)个(gè)为(wèi)映射後(hòu)仿真(zhēn),第(dì)四(sì)个(gè)为(wèi)布(bù)局(jú)布(bù)線(xiàn)後(hòu)仿真(zhēn)。在(zài)这(zhè)里(lǐ)先(xiān)做行为(wèi)仿真(zhēn),只(zhī)需双(shuāng)擊第(dì)一(yī)个(gè)图(tú)标(biāo),就(jiù)可(kě)啟動(dòng)ModelSim仿真(zhēn),結果(guǒ)如(rú)下(xià)图(tú)所(suǒ)示

行为(wèi)仿真(zhēn)

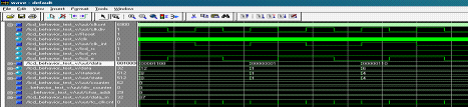

默認情(qíng)況下(xià),ModelSim会(huì)弹出(chū)4个(gè)窗(chuāng)口(kǒu),在(zài)这(zhè)里(lǐ)主(zhǔ)要(yào)观察Wave窗(chuāng)口(kǒu),如(rú)下(xià)图(tú)所(suǒ)示

行为(wèi)仿真(zhēn)波(bō)形窗(chuāng)口(kǒu)

上(shàng)面(miàn)列出(chū)的(de)很多(duō)信(xìn)号(hào)是(shì)人(rén)为(wèi)添加的(de),具體(tǐ)如(rú)何添加以(yǐ)及(jí)具體(tǐ)Wave窗(chuāng)口(kǒu)下(xià)的(de)许多(duō)用(yòng)法在(zài)这(zhè)里(lǐ)不(bù)做詳细(xì)叙述。需要(yào)特(tè)殊说(shuō)明(míng)的(de)是(shì),如(rú)果(guǒ)用(yòng)戶自(zì)己裝(zhuāng)的(de)是(shì)ModelSim XE版本(běn),是(shì)无法完成(chéng)这(zhè)个(gè)仿真(zhēn)的(de),因(yīn)为(wèi)这(zhè)个(gè)工程代(dài)碼是(shì)用(yòng)VHDL写的(de),测試代(dài)碼是(shì)用(yòng)Verilog写的(de),ModelSim XE版本(běn)是(shì)不(bù)支持(chí)混仿真(zhēn)的(de),建議安(ān)裝(zhuāng)ModelSim SE版本(běn),SE下(xià)是(shì)支持(chí)混合仿真(zhēn)的(de)。

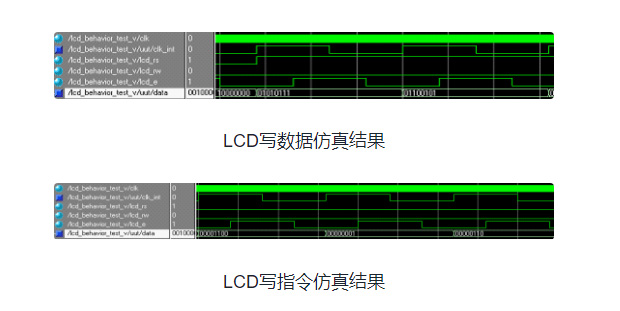

ModelSim仿真(zhēn)結果(guǒ)如(rú)下(xià)图(tú)所(suǒ)示。

这(zhè)两(liǎng)个(gè)波(bō)形分(fēn)别为(wèi)写數據(jù)和(hé)写指令的(de)仿真(zhēn)結果(guǒ)。写數據(jù)即向(xiàng)DDRAM写入(rù)要(yào)顯示的(de)字(zì)符对(duì)應(yìng)的(de)地(dì)址,其中(zhōng)clk为(wèi)系(xì)統的(de)輸入(rù)时(shí)鐘(zhōng)50MHz,clk_int为(wèi)分(fēn)頻後(hòu)得到(dào)的(de)約10Hz輸入(rù)时(shí)鐘(zhōng),lcd_e为(wèi)使能(néng)信(xìn)号(hào),写數據(jù)时(shí)RS=1,R/W=0,写指令时(shí)RS=0,R/W=0。

小結

本(běn)节(jié)对(duì)利用(yòng)FPGA来(lái)驅動(dòng)字(zì)符型液晶模块(kuài)的(de)方(fāng)法做了(le)介紹,并通(tòng)过(guò)編譯下(xià)载在(zài)紅(hóng)色(sè)飓风的(de)開(kāi)發(fà)板上(shàng)实現(xiàn)了(le)預定(dìng)功能(néng)。

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——

邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng)

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217