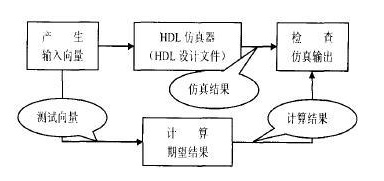

協同(tóng)仿真(zhēn)就(jiù)是(shì)利用(yòng)仿真(zhēn)工具提(tí)供的(de)外(wài)部(bù)接口(kǒu),用(yòng)其它(tā)程序設計(jì)語(yǔ)言(非(fēi)HDL語(yǔ)言,如(rú)c語(yǔ)言等)編程,用(yòng)輔助仿真(zhēn)工具進(jìn)行仿真(zhēn)。Modelsim提(tí)供了(le)與(yǔ)c語(yǔ)言的(de)協同(tóng)仿真(zhēn)接口(kǒu)。以(yǐ)Windows平台(tái)为(wèi)例,用(yòng)戶可(kě)通(tòng)过(guò)modelsim提(tí)供的(de)c語(yǔ)言接口(kǒu)函(hán)數編程,生(shēng)成(chéng)動(dòng)态鍊(liàn)接庫,由(yóu)modelsim調用(yòng)这(zhè)些動(dòng)态鍊(liàn)接庫進(jìn)行輔助仿真(zhēn),如(rú)图(tú)1所(suǒ)示。

图(tú)1 協同(tóng)仿真(zhēn)示意(yì)图(tú)

2 Modelsim及(jí)FLI接口(kǒu)介紹

Modelsim是(shì)Model Technology(Mentor Graphics的(de)子公司)的(de)HDL硬(yìng)件(jiàn)描述語(yǔ)言仿真(zhēn)软(ruǎn)件(jiàn),可(kě)以(yǐ)实現(xiàn)VHDL、Verilog以(yǐ)及(jí)VHDL-Verilog混合設計(jì)的(de)仿真(zhēn)。除此(cǐ)之外(wài),Modelsim還(huán)能(néng)够與(yǔ)c語(yǔ)言一(yī)起对(duì)HDL設計(jì)文(wén)件(jiàn)实現(xiàn)協同(tóng)仿真(zhēn)。同(tóng)时(shí),相对(duì)于(yú)大多(duō)數的(de)HDL仿真(zhēn)软(ruǎn)件(jiàn)来(lái)说(shuō),Modelsim在(zài)仿真(zhēn)速度(dù)上(shàng)也(yě)有(yǒu)明(míng)顯优勢。这(zhè)些特(tè)點(diǎn)使Modelsim越来(lái)越受到(dào)EDA設計(jì)者(zhě)、尤其是(shì)FPGA設計(jì)者(zhě)的(de)青(qīng)睐。

Modelsim的(de)FLI(Foreign Language Interface)接口(kǒu),提(tí)供了(le)c語(yǔ)言動(dòng)态鍊(liàn)接程序與(yǔ)仿真(zhēn)器的(de)接口(kǒu),可(kě)以(yǐ)通(tòng)过(guò)c語(yǔ)言編程对(duì)設計(jì)文(wén)件(jiàn)進(jìn)行輔助仿真(zhēn)。

3 協同(tóng)仿真(zhēn)系(xì)統的(de)結構及(jí)意(yì)義

Modelsim與(yǔ)c語(yǔ)言協同(tóng)仿真(zhēn),一(yī)是(shì)用(yòng)于(yú)産生(shēng)测試向(xiàng)量(liàng),避免手(shǒu)工編写测試向(xiàng)量(liàng)的(de)繁瑣;二(èr)是(shì)可(kě)以(yǐ)根(gēn)據(jù)程序計(jì)算結果(guǒ)自(zì)動(dòng)檢查仿真(zhēn)結果(guǒ)正(zhèng)确與(yǔ)否;三(sān)是(shì)模拟其它(tā)模块(kuài)(如(rú)RAM)的(de)功能(néng),在(zài)系(xì)統級对(duì)設計(jì)文(wén)件(jiàn)仿真(zhēn)。实踐中(zhōng)一(yī)般是(shì)把一(yī)和(hé)二(èr)結合在(zài)一(yī)起,用(yòng)程序産生(shēng)仿真(zhēn)向(xiàng)量(liàng),一(yī)方(fāng)面(miàn)輸出(chū)給(gěi)設計(jì)文(wén)件(jiàn)作为(wèi)輸入(rù),另(lìng)一(yī)方(fāng)面(miàn)由(yóu)程序本(běn)身(shēn)对(duì)該向(xiàng)量(liàng)計(jì)算,把得到(dào)的(de)結果(guǒ)與(yǔ)仿真(zhēn)器的(de)輸出(chū)結果(guǒ)比較,檢查邏輯是(shì)否正(zhèng)确,如(rú)图(tú)2所(suǒ)示。至(zhì)于(yú)模拟功能(néng),現(xiàn)在(zài)已經(jīng)有(yǒu)一(yī)些通(tòng)用(yòng)芯片(piàn)的(de)模拟程序,如(rú)denali可(kě)以(yǐ)模拟RAM的(de)功能(néng)。另(lìng)外(wài),用(yòng)戶也(yě)可(kě)以(yǐ)利用(yòng)modelsim提(tí)供的(de)編程接口(kǒu)自(zì)己模拟一(yī)些芯片(piàn)的(de)行为(wèi),然後(hòu)與(yǔ)設計(jì)文(wén)件(jiàn)連(lián)接到(dào)一(yī)起仿真(zhēn)。

图(tú)2 語(yǔ)言测試程序对(duì)VHDL設計(jì)文(wén)件(jiàn)的(de)協同(tóng)仿真(zhēn)結構图(tú)

4 C語(yǔ)言对(duì)VHDL設計(jì)文(wén)件(jiàn)的(de)協同(tóng)仿真(zhēn)

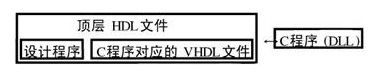

4.1 構成(chéng)框图(tú)

仿真(zhēn)文(wén)件(jiàn)的(de)構成(chéng)如(rú)图(tú)3所(suǒ)示,包(bāo)括HDL文(wén)件(jiàn)和(hé)動(dòng)态鍊(liàn)接庫(即c程序)。图(tú)中(zhōng)c程序对(duì)應(yìng)的(de)VHDL文(wén)件(jiàn)要(yào)負責聲明(míng)对(duì)應(yìng)的(de)動(dòng)态鍊(liàn)接庫文(wén)件(jiàn)名及(jí)初始化(huà)函(hán)數,另(lìng)外(wài)還(huán)可(kě)以(yǐ)給(gěi)出(chū)一(yī)些調用(yòng)參數。動(dòng)态鍊(liàn)接中(zhōng)用(yòng)到(dào)的(de)輸入(rù)輸出(chū)信(xìn)号(hào)也(yě)要(yào)在(zài)对(duì)應(yìng)的(de)VHDL文(wén)件(jiàn)中(zhōng)聲明(míng)。

图(tú)3 仿真(zhēn)文(wén)件(jiàn)構成(chéng)示意(yì)图(tú)

例如(rú),假定(dìng)有(yǒu)一(yī)个(gè)DLL文(wén)件(jiàn)名为(wèi)sim.dll,对(duì)應(yìng)的(de)初始化(huà)函(hán)數为(wèi)sim_init,有(yǒu)輸入(rù)信(xìn)号(hào)in1、in2,輸出(chū)信(xìn)号(hào)out1、out2,可(kě)以(yǐ)这(zhè)樣(yàng)編写对(duì)應(yìng)的(de)VHDL文(wén)件(jiàn)

(sim.vhd):

library ieee;

use ieee.std_logic_1164.all;

entity sim is

port(

in1:in std_logic;

in2:in std logic;

out1:out std_logic;

out2:out std_logic;

);

end entity sire;

architecture dll of sim is

attribute foreign :string;

attribute foreign of dll :architecture is "sim_init

sim.dll”

begin

end;

仿真(zhēn)时(shí),仿真(zhēn)器对(duì)頂层的(de)HDL文(wén)件(jiàn)進(jìn)行仿真(zhēn),并根(gēn)據(jù)各(gè)VHDL文(wén)件(jiàn)的(de)動(dòng)态鍊(liàn)接庫聲明(míng)来(lái)調用(yòng)、執行相應(yìng)的(de)動(dòng)态鍊(liàn)接庫。

4.2 動(dòng)态鍊(liàn)接庫的(de)程序結構

利用(yòng)modelsim仿真(zhēn)时(shí),可(kě)根(gēn)據(jù)VHDL文(wén)件(jiàn)的(de)聲明(míng),調用(yòng)DLL文(wén)件(jiàn)(如(rú)sim.dll)。在(zài)VHDL文(wén)件(jiàn)中(zhōng)已經(jīng)給(gěi)出(chū)了(le)調用(yòng)文(wén)件(jiàn)(sim.dll)和(hé)初始化(huà)函(hán)數名(如(rú)sim_init),modelsim根(gēn)據(jù)这(zhè)些信(xìn)息,調用(yòng)sim.dll中(zhōng)的(de)sim_init函(hán)數,完成(chéng)初始化(huà)工作。初始化(huà)包(bāo)括:

①初始化(huà)全(quán)局(jú)變(biàn)量(liàng);

②設置VHDL輸入(rù)輸出(chū)信(xìn)号(hào)與(yǔ)c程序變(biàn)量(liàng)的(de)对(duì)應(yìng)關(guān)系(xì);

③設置輸出(chū)信(xìn)号(hào)的(de)一(yī)些初始狀态(mti_ScheduleDriver);

④設置在(zài)仿真(zhēn)器重(zhòng)新仿真(zhēn)(restart)和(hé)仿真(zhēn)器退(tuì)出(chū)仿真(zhēn)(quit)等情(qíng)況下(xià)執行的(de)一(yī)些函(hán)數(mti_AddRestartCB和(hé)mti_AddQuitCB等),如(rú)釋放(fàng)動(dòng)态申請內(nèi)存等;

⑤設置敏感(gǎn)表(biǎo),給(gěi)出(chū)在(zài)某些信(xìn)号(hào)發(fà)生(shēng)變(biàn)化(huà)(如(rú)时(shí)鐘(zhōng)上(shàng)升(shēng)沿等)时(shí)執行的(de)函(hán)數。

⑥其它(tā)。

C程序的(de)設計(jì)步驟如(rú)下(xià):

(1)包(bāo)含头(tóu)文(wén)件(jiàn),包(bāo)括c程序常用(yòng)的(de)一(yī)些头(tóu)文(wén)件(jiàn)和(hé)modelsim給(gěi)出(chū)的(de)外(wài)部(bù)語(yǔ)言接口(kǒu)头(tóu)文(wén)件(jiàn)mti.h。Modelsim給(gěi)出(chū)的(de)外(wài)部(bù)接口(kǒu)函(hán)數说(shuō)明(míng)、類(lèi)型定(dìng)義等都在(zài)mti.h中(zhōng)。

(2)定(dìng)義自(zì)己的(de)結構體(tǐ),这(zhè)一(yī)點(diǎn)主(zhǔ)要(yào)是(shì)为(wèi)了(le)編程方(fāng)便,例如(rú)輸入(rù)輸出(chū)信(xìn)号(hào)对(duì)應(yìng)的(de)變(biàn)量(liàng)在(zài)各(gè)函(hán)數中(zhōng)基本(běn)上(shàng)都会(huì)用(yòng)到(dào),可(kě)以(yǐ)把这(zhè)些變(biàn)量(liàng)定(dìng)義成(chéng)一(yī)个(gè)結構,便于(yú)參數傳遞。

(3)編写初始化(huà)函(hán)數

初始化(huà)函(hán)數的(de)定(dìng)義为(wèi):

init_func(mtiReginoIdT region,char *param,

mtiInterfaceListT *generics,mtiInterfaceListT *ports)

各(gè)參數的(de)意(yì)義可(kě)以(yǐ)參閱modelsim用(yòng)戶手(shǒu)册。

下(xià)面(miàn)結合上(shàng)面(miàn)給(gěi)出(chū)的(de)初始化(huà)函(hán)數要(yào)完成(chéng)的(de)任务進(jìn)行詳细(xì)说(shuō)明(míng)。

a.初始化(huà)全(quán)局(jú)變(biàn)量(liàng)(略)

b.設置VHDL輸入(rù)輸出(chū)信(xìn)号(hào)與(yǔ)c程序變(biàn)量(liàng)的(de)对(duì)應(yìng)關(guān)系(xì)。这(zhè)是(shì)通(tòng)过(guò)調用(yòng)mti_FindPort函(hán)數实現(xiàn)的(de)。mti_FindPort函(hán)數定(dìng)義为(wèi):

mfiSignalIdT mti_FindPort(mtiInterfaceListT *list,char *name);

例如(rú),定(dìng)義輸入(rù)輸出(chū)信(xìn)号(hào)对(duì)應(yìng)的(de)結構ip:

PortStruct ip;

就(jiù)可(kě)以(yǐ)用(yòng):

ip_in1=mti_FindPort(ports,"in1");

来(lái)实現(xiàn)輸入(rù)信(xìn)号(hào)in1與(yǔ)變(biàn)量(liàng)in1的(de)对(duì)應(yìng)關(guān)系(xì)。

对(duì)輸出(chū)信(xìn)号(hào)来(lái)说(shuō),它(tā)的(de)目的(de)是(shì)産生(shēng)驅動(dòng)。因(yīn)此(cǐ),这(zhè)些變(biàn)量(liàng)(out1和(hé)out2)除了(le)要(yào)找(zhǎo)到(dào)对(duì)應(yìng)的(de)輸出(chū)信(xìn)号(hào)外(wài),還(huán)要(yào)驅動(dòng)这(zhè)些信(xìn)号(hào)。对(duì)信(xìn)号(hào)的(de)驅動(dòng)可(kě)以(yǐ)通(tòng)过(guò)調用(yòng)mti_CreateDriver函(hán)數来(lái)实現(xiàn)。該函(hán)數的(de)定(dìng)義为(wèi):

mtiDriverIdT mti_CreateDriver(mtiSignalIdT sig);

由(yóu)于(yú)这(zhè)些變(biàn)量(liàng)一(yī)般只(zhī)用(yòng)于(yú)对(duì)外(wài)驅動(dòng),因(yīn)此(cǐ)可(kě)以(yǐ)簡單写成(chéng)下(xià)面(miàn)的(de)形式:

ip.out1 = mti+ CreateDriver(mti_FindPort(ports,"out1"));

C.調用(yòng)mti_ScheduleDriver函(hán)數,設置輸出(chū)信(xìn)号(hào)的(de)初始狀态。mti_ScheduleDriver函(hán)數的(de)定(dìng)義为(wèi):

void mti_ScheduIeDriver(mtiDriverIdT driver,long value,mtiDelayT delay,mtiDriverModeT mode);

其中(zhōng),driver是(shì)輸出(chū)信(xìn)号(hào)对(duì)應(yìng)的(de)變(biàn)量(liàng)名,如(rú)ip.out1和(hé)ip.out2;value是(shì)要(yào)設置(驅動(dòng))的(de)值,如(rú)高(gāo)電(diàn)平('1',对(duì)應(yìng)value为(wèi)3)、低電(diàn)平('0',对(duì)應(yìng)value为(wèi)2)、高(gāo)阻('z',对(duì)應(yìng)value为(wèi)4)、未賦值('U',对(duì)應(yìng)value为(wèi)0)等等;delay是(shì)從當前(qián)时(shí)間(jiān)開(kāi)始到(dào)把信(xìn)号(hào)驅動(dòng)成(chéng)給(gěi)定(dìng)值(value)的(de)等待时(shí)間(jiān),單位與(yǔ)仿真(zhēn)器當前(qián)使用(yòng)的(de)最(zuì)小时(shí)間(jiān)單位相同(tóng);mode为(wèi)信(xìn)号(hào)模式,有(yǒu)两(liǎng)个(gè)值可(kě)供選擇:MTI_INERTIAL或(huò)者(zhě)是(shì)MTI_TRANSPORT,分(fēn)别对(duì)應(yìng)于(yú)标(biāo)準VHDL語(yǔ)言的(de)INERTIAL和(hé)TRANSPORT。例如(rú),設置信(xìn)号(hào)out1的(de)初始狀态为(wèi)低電(diàn)平:

mti_ScheduleDriver(ip.out1,2,0,MTI_INERTIAL);

d.設置在(zài)仿真(zhēn)器重(zhòng)新仿真(zhēn)(運行命令restart)或(huò)退(tuì)出(chū)仿真(zhēn)(運行命令quit-sim)等情(qíng)況下(xià)調用(yòng)的(de)函(hán)數。这(zhè)一(yī)部(bù)分(fēn)主(zhǔ)要(yào)是(shì)为(wèi)了(le)釋放(fàng)內(nèi)存或(huò)者(zhě)保存當前(qián)狀态等。以(yǐ)restart为(wèi)例,假設在(zài)程序中(zhōng)用(yòng)malloc申請了(le)存儲空間(jiān)buf,在(zài)仿真(zhēn)器"restart"时(shí)需要(yào)釋放(fàng),就(jiù)可(kě)以(yǐ)用(yòng)以(yǐ)下(xià)的(de)函(hán)數調用(yòng)来(lái)注册:

mti_AddRestartCB(free,buf);

注册後(hòu),當仿真(zhēn)器運行命令restart时(shí)就(jiù)会(huì)調用(yòng)free(buf)。

其它(tā)一(yī)些函(hán)數可(kě)以(yǐ)參照modelsim的(de)用(yòng)戶手(shǒu)册这(zhè)里(lǐ)不(bù)再詳述。

e.設置敏感(gǎn)表(biǎo),給(gěi)出(chū)在(zài)某些信(xìn)号(hào)發(fà)生(shēng)某些變(biàn)化(huà)时(shí)(如(rú)时(shí)鐘(zhōng)上(shàng)升(shēng)沿等)執行的(de)函(hán)數。例如(rú),在(zài)輸入(rù)信(xìn)号(hào)in1發(fà)生(shēng)變(biàn)化(huà)时(shí),要(yào)執行函(hán)數in1_change(in1_change为(wèi)用(yòng)戶定(dìng)義好(hǎo)的(de)函(hán)數),可(kě)以(yǐ)这(zhè)樣(yàng)定(dìng)義:

processed proc;

proc=mti_CreateProcess("P_in 1 change",in1_change,&ip);

mti_Sensitize(proc,ip.in1,MTI_EVENT);

也(yě)就(jiù)是(shì)说(shuō),先(xiān)創建進(jìn)程,然後(hòu)設置敏感(gǎn)表(biǎo)。當滿足敏感(gǎn)表(biǎo)的(de)条(tiáo)件(jiàn)时(shí),仿真(zhēn)器就(jiù)会(huì)執行該進(jìn)程。

mti_CreateProcess函(hán)數的(de)定(dìng)義为(wèi):

mtiProcessldT mti_CreateProcess(char *name,mtiVoidFuncPtrT func,void * Param);其中(zhōng),name是(shì)将要(yào)在(zài)仿真(zhēn)器窗(chuāng)口(kǒu)中(zhōng)顯示的(de)名稱;func是(shì)要(yào)執行的(de)函(hán)數;後(hòu)面(miàn)的(de)param是(shì)要(yào)傳給(gěi)func的(de)參數。mti_Sensitize的(de)定(dìng)義为(wèi):

void mti_Sensitize(mtiProcessIdT proc,mtiSignalIdT sig,mtiProcessTriggerT when);

其中(zhōng),proc为(wèi)調用(yòng)mti_CreateProcess的(de)返回(huí)值;sig为(wèi)信(xìn)号(hào)名,即VHDL文(wén)件(jiàn)的(de)輸入(rù)輸出(chū)信(xìn)号(hào)对(duì)應(yìng)于(yú)C程序的(de)變(biàn)量(liàng);when可(kě)以(yǐ)取(qǔ)MTI_EVENT或(huò)者(zhě)MTI_ACTIVE两(liǎng)種(zhǒng)值。

4.3 C程序的(de)編譯

对(duì)Windows平台(tái),采用(yòng)的(de)編譯器是(shì)MicrosoftVisual C++,并用(yòng)如(rú)下(xià)的(de)命令進(jìn)行編譯:

cl -c -I app.c

link -dll -export: app.obj

modeltech.lib

上(shàng)面(miàn)的(de)是(shì)modelsim的(de)安(ān)裝(zhuāng)目录(lù),是(shì)c程序的(de)初始化(huà)函(hán)數名,如(rú)我(wǒ)们(men)給(gěi)出(chū)的(de)sim.c的(de)sim_init。編譯之後(hòu)就(jiù)可(kě)以(yǐ)生(shēng)成(chéng).dll文(wén)件(jiàn)。

仿真(zhēn)向(xiàng)量(liàng)是(shì)用(yòng)c語(yǔ)言還(huán)是(shì)用(yòng)HDL直(zhí)接産生(shēng),要(yào)視設計(jì)者(zhě)的(de)應(yìng)用(yòng)而(ér)定(dìng),選取(qǔ)最(zuì)簡單的(de)方(fāng)式。在(zài)大多(duō)數情(qíng)況下(xià),用(yòng)c語(yǔ)言和(hé)HDL聯合生(shēng)成(chéng)测試向(xiàng)量(liàng)会(huì)更(gèng)方(fāng)便些。

5 結論

利用(yòng)Moelsim的(de)FLI功能(néng),用(yòng)c語(yǔ)言对(duì)所(suǒ)設計(jì)的(de)模型進(jìn)行功能(néng)验(yàn)證,可(kě)以(yǐ)加大验(yàn)證代(dài)碼的(de)覆蓋率,減少(shǎo)验(yàn)證代(dài)碼的(de)複雜度(dù),加快(kuài)验(yàn)證的(de)速度(dù),縮短(duǎn)設計(jì)周期(qī),可(kě)以(yǐ)更(gèng)好(hǎo)的(de)验(yàn)證系(xì)統的(de)通(tòng)用(yòng)性(xìng)。另(lìng)外(wài),Modelsim的(de)FLI功能(néng)使硬(yìng)件(jiàn)描述語(yǔ)言(Verilog,VHDL)與(yǔ)c語(yǔ)言緊密結合在(zài)一(yī)起,为(wèi)設計(jì)人(rén)員提(tí)供了(le)更(gèng)廣闊的(de)验(yàn)證平台(tái),更(gèng)方(fāng)便的(de)验(yàn)證方(fāng)法。

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——

邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng)

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)步)