本(běn)白皮書(shū)讨論各(gè)種(zhǒng)存儲器接口(kǒu)控制器設計(jì)所(suǒ)面(miàn)臨的(de)挑戰和(hé) Xilinx 的(de)解(jiě)決方(fāng)案(àn),同(tóng)时(shí)也(yě)说(shuō)明(míng)如(rú)何使用(yòng) Xilinx软(ruǎn)件(jiàn)工具和(hé)經(jīng)过(guò)硬(yìng)件(jiàn)验(yàn)證的(de)參考設計(jì)来(lái)为(wèi)您自(zì)己的(de)應(yìng)用(yòng)(從低成(chéng)本(běn)的(de) DDR SDRAM 應(yìng)用(yòng)到(dào)像 667 Mb/sDDR2 SDRAM 这(zhè)樣(yàng)的(de)更(gèng)高(gāo)性(xìng)能(néng)接口(kǒu))設計(jì)完整的(de)存

儲器接口(kǒu)解(jiě)決方(fāng)案(àn)。

存儲器接口(kǒu)趨勢和(hé) Xilinx 解(jiě)決方(fāng)案(àn)

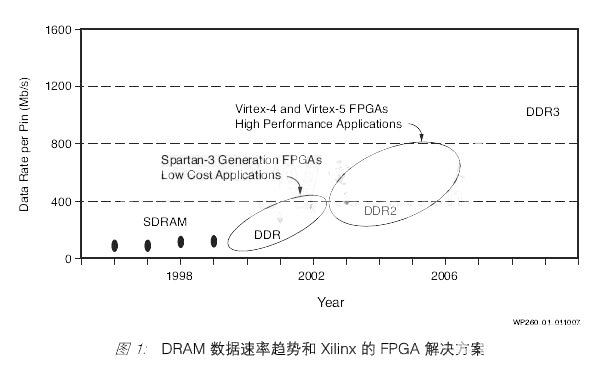

20 世紀 90 年(nián)代(dài)後(hòu)期(qī),存儲器接口(kǒu)從單倍數據(jù)速率 (SDR) SDRAM 發(fà)展(zhǎn)到(dào)了(le)双(shuāng)倍數據(jù)速率 (DDR) SDRAM,而(ér)今天(tiān)的(de) DDR2 SDRAM 運行速率已經(jīng)达(dá)到(dào)每引脚 667 Mb/s或(huò)更(gèng)高(gāo)。當今的(de)趨勢顯示,这(zhè)些數據(jù)速率可(kě)能(néng)每四(sì)年(nián)增加一(yī)倍,到(dào) 2010 年(nián),随着DDR3 SDRAM 的(de)出(chū)現(xiàn),很可(kě)能(néng)超过(guò)每引脚 1.2 Gb/s。見(jiàn)图(tú)1。

應(yìng)用(yòng)通(tòng)常可(kě)分(fēn)为(wèi)两(liǎng)類(lèi):一(yī)類(lèi)是(shì)低成(chéng)本(běn)應(yìng)用(yòng),降低器件(jiàn)成(chéng)本(běn)为(wèi)主(zhǔ)要(yào)目的(de);另(lìng)一(yī)類(lèi)是(shì)高(gāo)性(xìng)能(néng)應(yìng)用(yòng),首要(yào)目标(biāo)是(shì)谋求高(gāo)带(dài)宽(kuān)。

運行速率低于(yú)每引脚 400 Mb/s 的(de) DDR SDRAM 和(hé)低端 DDR2 SDRAM 已能(néng)滿足大多(duō)數低成(chéng)本(běn)系(xì)統存儲器的(de)带(dài)宽(kuān)需求。对(duì)于(yú)这(zhè)類(lèi)應(yìng)用(yòng),Xilinx 提(tí)供了(le) Spartan-3 系(xì)列FPGA,其中(zhōng)包(bāo)括 Spartan-3、Spartan-3E 和(hé) Spartan-3A 器件(jiàn)。

高(gāo)性(xìng)能(néng)應(yìng)用(yòng)把每引脚 533 和(hé) 667 Mb/s 的(de) DDR2 SDRAM 这(zhè)樣(yàng)的(de)存儲器接口(kǒu)带(dài)宽(kuān)推到(dào)了(le)极(jí)限;对(duì)于(yú)这(zhè)類(lèi)應(yìng)用(yòng),Xilinx 推出(chū)了(le) Virtex-4 和(hé) Virtex-5 FPGA,能(néng)够充分(fēn)滿足今天(tiān)大多(duō)數系(xì)統的(de)最(zuì)高(gāo)带(dài)宽(kuān)需求。

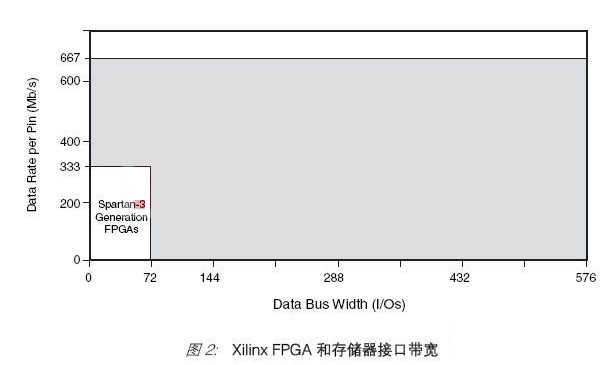

带(dài)宽(kuān)是(shì)與(yǔ)每引脚數據(jù)速率和(hé)數據(jù)總(zǒng)線(xiàn)宽(kuān)度(dù)相關(guān)的(de)一(yī)个(gè)因(yīn)素。Spartan-3 系(xì)列、Virtex-4、Virtex-5 FPGA 提(tí)供不(bù)同(tóng)的(de)選項,從數據(jù)總(zǒng)線(xiàn)宽(kuān)度(dù)小于(yú) 72 位的(de)較小的(de)低成(chéng)本(běn)統,

到(dào)576 位宽(kuān)的(de)更(gèng)大的(de) Virtex-5 封(fēng)裝(zhuāng)(見(jiàn)图(tú)2)。

高(gāo)于(yú) 400 Mb/s 速率的(de)更(gèng)宽(kuān)總(zǒng)線(xiàn)使得芯片(piàn)到(dào)芯片(piàn)的(de)接口(kǒu)愈益難以(yǐ)開(kāi)發(fà),因(yīn)为(wèi)需要(yào)更(gèng)大的(de)封(fēng)裝(zhuāng)、更(gèng)好(hǎo)的(de)電(diàn)源和(hé)接地(dì)-信(xìn)号(hào)比率。Virtex-4 和(hé) Virtex-5 FPGA 的(de)開(kāi)發(fà)使用(yòng)了(le)先(xiān)進(jìn)的(de)稀疏鋸齒形 (Sparse ChevrON) 封(fēng)裝(zhuāng)技術(shù),能(néng)提(tí)供优良的(de)信(xìn)号(hào)-電(diàn)源和(hé)接地(dì)引脚比率。每个(gè) I/O 引脚周圍都有(yǒu)足够的(de)電(diàn)源和(hé)接地(dì)引脚和(hé)板,以(yǐ)确保良好(hǎo)的(de)屏蔽,使由(yóu)同(tóng)步交換輸出(chū) (SSO) 所(suǒ)造成(chéng)的(de)串擾噪音(yīn)降到(dào)最(zuì)低。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)步)