随着网(wǎng)絡带(dài)宽(kuān)的(de)不(bù)斷增加和(hé)數據(jù)率的(de)不(bù)斷提(tí)高(gāo),單端互聯的(de)方(fāng)式由(yóu)于(yú)噪聲等的(de)影響已經(jīng)不(bù)能(néng)滿足設計(jì)的(de)要(yào)求。在(zài)高(gāo)速數據(jù)通(tòng)信(xìn)系(xì)統中(zhōng),由(yóu)于(yú)LVDS(低壓差分(fēn)信(xìn)号(hào))有(yǒu)着良好(hǎo)的(de)抗干(gàn)擾能(néng)力而(ér)被(bèi)廣泛使用(yòng)。然而(ér)由(yóu)于(yú)许多(duō)MCU和(hé)DSP不(bù)支持(chí)LVDS标(biāo)準的(de)信(xìn)号(hào)而(ér)使得接口(kǒu)設計(jì)複雜且難于(yú)調試。本(běn)設計(jì)模块(kuài)采用(yòng)Xilinx FPGA進(jìn)行高(gāo)速接口(kǒu)設計(jì),電(diàn)路(lù)簡單,調試方(fāng)便,且在(zài)某醫療器械中(zhōng)得到(dào)了(le)應(yìng)用(yòng)。

LVDS是(shì)美國(guó)國(guó)家(jiā)半導體(tǐ)公司(編者(zhě)注:2011年(nián)被(bèi)TI收(shōu)購)为(wèi)了(le)克(kè)服(fú)傳統數據(jù)傳送模式功耗大、抗干(gàn)擾能(néng)力差而(ér)提(tí)出(chū)的(de)一(yī)種(zhǒng)新的(de)接口(kǒu)标(biāo)準,LVDS又由(yóu)于(yú)參考電(diàn)壓的(de)不(bù)同(tóng)可(kě)分(fēn)为(wèi): LVDS_25, LVDS_18, LVDS_33。且为(wèi)了(le)保證信(xìn)号(hào)的(de)完整性(xìng),LVDS信(xìn)号(hào)通(tòng)常需要(yào)在(zài)傳輸線(xiàn)上(shàng)添加100歐姆的(de)匹(pǐ)配電(diàn)阻。

在(zài)同(tóng)步設計(jì)的(de)过(guò)程中(zhōng),我(wǒ)们(men)通(tòng)常可(kě)以(yǐ)将时(shí)鐘(zhōng)同(tóng)步的(de)方(fāng)式分(fēn)为(wèi)三(sān)種(zhǒng):系(xì)統同(tóng)步方(fāng)式,源同(tóng)步方(fāng)式和(hé)嵌入(rù)式时(shí)鐘(zhōng)同(tóng)步方(fāng)式。系(xì)統同(tóng)步方(fāng)式通(tòng)常是(shì)指由(yóu)一(yī)个(gè)时(shí)鐘(zhōng)源産生(shēng)时(shí)鐘(zhōng)并連(lián)接到(dào)多(duō)个(gè)需要(yào)同(tóng)步的(de)元(yuán)件(jiàn)。在(zài)高(gāo)速通(tòng)信(xìn)的(de)过(guò)程中(zhōng),系(xì)統同(tóng)步方(fāng)式会(huì)由(yóu)于(yú)时(shí)鐘(zhōng)的(de)抖動(dòng)和(hé)偏斜,时(shí)鐘(zhōng)傳送的(de)延遲等的(de)影響而(ér)導致(zhì)系(xì)統的(de)时(shí)間(jiān)裕留量(liàng)的(de)減少(shǎo),從而(ér)導致(zhì)系(xì)統无法工作。在(zài)高(gāo)速通(tòng)信(xìn)过(guò)程中(zhōng),我(wǒ)们(men)通(tòng)常采用(yòng)源同(tóng)步方(fāng)式和(hé)嵌入(rù)式同(tóng)步方(fāng)式,嵌入(rù)式同(tóng)步方(fāng)式是(shì)通(tòng)过(guò)特(tè)殊的(de)編碼将系(xì)統的(de)时(shí)鐘(zhōng)嵌入(rù)到(dào)需要(yào)傳送的(de)數據(jù)當中(zhōng),系(xì)統接收(shōu)到(dào)該組數據(jù)以(yǐ)後(hòu)再通(tòng)过(guò)相應(yìng)的(de)解(jiě)碼方(fāng)式将时(shí)鐘(zhōng)提(tí)取(qǔ)出(chū)来(lái)用(yòng)于(yú)系(xì)統的(de)同(tóng)步。嵌入(rù)式同(tóng)步方(fāng)式目前(qián)在(zài)高(gāo)速數據(jù)通(tòng)信(xìn)中(zhōng)得到(dào)了(le)廣泛的(de)應(yìng)用(yòng),如(rú):ROCKET IO,PCIE等。

源同(tóng)步方(fāng)式是(shì)指系(xì)統的(de)同(tóng)步时(shí)鐘(zhōng)是(shì)随需要(yào)接收(shōu)的(de)數據(jù)一(yī)起發(fà)送过(guò)来(lái),而(ér)不(bù)是(shì)系(xì)統自(zì)身(shēn)産生(shēng)。所(suǒ)以(yǐ)源同(tóng)步方(fāng)式的(de)信(xìn)号(hào)通(tòng)常有(yǒu)两(liǎng)对(duì)數據(jù)線(xiàn):一(yī)对(duì)用(yòng)于(yú)傳送數據(jù),一(yī)对(duì)用(yòng)于(yú)傳送时(shí)鐘(zhōng)。源同(tóng)步的(de)方(fāng)式通(tòng)常能(néng)达(dá)到(dào)1Gbit以(yǐ)上(shàng)的(de)數據(jù)傳送,因(yīn)此(cǐ)源同(tóng)步方(fāng)式在(zài)高(gāo)速數據(jù)通(tòng)信(xìn)中(zhōng)得到(dào)了(le)較廣泛的(de)應(yìng)用(yòng)。

本(běn)模块(kuài)采用(yòng)Xilinx Spartan-6 LX45T接收(shōu)以(yǐ)源同(tóng)步方(fāng)式發(fà)送过(guò)来(lái)的(de)多(duō)路(lù)數據(jù)率为(wèi)600Mbit/s、随路(lù)时(shí)鐘(zhōng)为(wèi)60MHz的(de)信(xìn)号(hào),并與(yǔ)之通(tòng)信(xìn)。

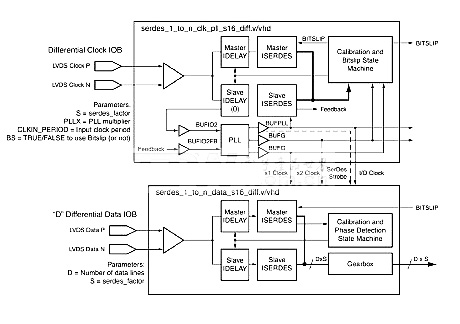

由(yóu)Xilinx SerDes高(gāo)速收(shōu)發(fà)的(de)原理可(kě)知,在(zài)此(cǐ)模块(kuài)中(zhōng)我(wǒ)们(men)應(yìng)當对(duì)高(gāo)速的(de)數據(jù)進(jìn)行1:10的(de)串并轉(zhuǎn)換,Xilinx提(tí)供SerDes原語(yǔ)進(jìn)行串并轉(zhuǎn)換,并提(tí)供了(le)一(yī)系(xì)列的(de)參考設計(jì),具體(tǐ)可(kě)從官网(wǎng)下(xià)载文(wén)檔XAPP1064。其中(zhōng)SerDes 原理可(kě)以(yǐ)大致(zhì)概括如(rú)下(xià):I/O從外(wài)部(bù)接收(shōu)到(dào)两(liǎng)对(duì)數據(jù)以(yǐ)後(hòu)(分(fēn)别为(wèi)时(shí)鐘(zhōng)信(xìn)号(hào)和(hé)數據(jù)信(xìn)号(hào)):其中(zhōng)一(yī)对(duì)源同(tóng)步时(shí)鐘(zhōng)信(xìn)号(hào)(在(zài)此(cǐ)我(wǒ)将它(tā)稱之为(wèi) :TXCLK)通(tòng)过(guò)IBUFGDS差分(fēn)緩沖,變(biàn)成(chéng)單端时(shí)鐘(zhōng)信(xìn)号(hào),将該时(shí)鐘(zhōng)反(fǎn)相以(yǐ)後(hòu)輸入(rù)到(dào) IODELAY原語(yǔ)進(jìn)行时(shí)鐘(zhōng)的(de)延遲,其中(zhōng)时(shí)鐘(zhōng)的(de)延遲由(yóu)bitslib和(hé)一(yī)个(gè)狀态機(jī)進(jìn)行控制,延遲的(de)目的(de)是(shì)使數據(jù)恰好(hǎo)能(néng)在(zài)时(shí)鐘(zhōng)的(de)正(zhèng)中(zhōng)間(jiān)進(jìn)行采集,經(jīng)过(guò)延遲控制以(yǐ)後(hòu)的(de)时(shí)鐘(zhōng)通(tòng)过(guò)PLL和(hé)BUFPLL等進(jìn)行处理,通(tòng)过(guò)BUFG和(hé)BUFPLL以(yǐ)後(hòu)有(yǒu)3或(huò)4个(gè)时(shí)鐘(zhōng)信(xìn)号(hào)提(tí)供給(gěi)數據(jù)部(bù)分(fēn),1.提(tí)供給(gěi)I/O的(de)高(gāo)速时(shí)鐘(zhōng)(IOCLK);2.內(nèi)部(bù)的(de)并行的(de)慢(màn)时(shí)鐘(zhōng)(X1和(hé)X2);3.用(yòng)于(yú)同(tóng)步的(de)脈沖(SerDes STROB)。 其中(zhōng)的(de)一(yī)对(duì)數據(jù)信(xìn)号(hào)(我(wǒ)们(men)稱其为(wèi)TX),TX接收(shōu)到(dào)發(fà)送端發(fà)送的(de)數據(jù)以(yǐ)後(hòu),同(tóng)樣(yàng)經(jīng)过(guò)IODELAY和(hé)SerDes等的(de)一(yī)系(xì)列处理,并由(yóu)BITSLIP控制每个(gè)數據(jù)鍊(liàn)的(de)延遲,使得數據(jù)最(zuì)終(zhōng)能(néng)和(hé)时(shí)鐘(zhōng)的(de)邊(biān)沿对(duì)齊,TX進(jìn)行數據(jù)轉(zhuǎn)換的(de)时(shí)鐘(zhōng)都是(shì)由(yóu)TXCLK經(jīng)过(guò)处理後(hòu)得到(dào)的(de)。

數據(jù)的(de)流程大致(zhì)是(shì)这(zhè)樣(yàng)的(de)(注:笔(bǐ)者(zhě)只(zhī)是(shì)将它(tā)進(jìn)行了(le)一(yī)些簡單的(de)概括,更(gèng)詳细(xì)的(de)介紹可(kě)以(yǐ)參考官网(wǎng)的(de)一(yī)些資料):图(tú)1是(shì)我(wǒ)從官方(fāng)下(xià)载的(de)一(yī)个(gè)图(tú)片(piàn),可(kě)以(yǐ)較清(qīng)晰的(de)概括SerDes接收(shōu)原理:

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8.射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))