本(běn)文(wén)我(wǒ)们(men)介紹利用(yòng)FPGA实現(xiàn)VGA图(tú)像顯示,主(zhǔ)要(yào)介紹VGA硬(yìng)件(jiàn)接口(kǒu)、VGA接口(kǒu)时(shí)序原理以(yǐ)及(jí)FPGA代(dài)碼实現(xiàn)VGA接口(kǒu)时(shí)序、仿真(zhēn)等內(nèi)容。

01、VGA硬(yìng)件(jiàn)接口(kǒu)介紹

VGA(Video Graphics Array)視頻图(tú)形阵(zhèn)列是(shì)IBM于(yú)1987年(nián)提(tí)出(chū)的(de)一(yī)个(gè)使用(yòng)模拟信(xìn)号(hào)的(de)電(diàn)腦顯示标(biāo)準。

VGA接口(kǒu)即電(diàn)腦采用(yòng)VGA标(biāo)準輸出(chū)數據(jù)的(de)專用(yòng)接口(kǒu)。VGA接口(kǒu)共(gòng)有(yǒu)15針(zhēn),分(fēn)成(chéng)3排,每排5个(gè)孔,顯卡(kǎ)上(shàng)應(yìng)用(yòng)最(zuì)为(wèi)廣泛的(de)接口(kǒu)類(lèi)型,絕大多(duō)數顯卡(kǎ)都带(dài)有(yǒu)此(cǐ)種(zhǒng)接口(kǒu)。

它(tā)傳輸紅(hóng)、綠(lǜ)、藍(lán)模拟信(xìn)号(hào)以(yǐ)及(jí)同(tóng)步信(xìn)号(hào)(水(shuǐ)平和(hé)垂直(zhí)信(xìn)号(hào))。

图(tú)1-VGA接口(kǒu)

|

管(guǎn)脚 |

信(xìn)号(hào) |

信(xìn)号(hào)描述 |

| 1 |

RED |

紅(hóng)基色(sè) |

| 2 |

GREEN |

綠(lǜ)基色(sè) |

| 3 |

BLUE |

藍(lán)基色(sè) |

| 4 |

ADDR_CODE |

地(dì)址碼 |

| 5 |

RES |

自(zì)测試(各(gè)家(jiā)定(dìng)義不(bù)同(tóng)) |

| 6 |

RED_GND |

紅(hóng)地(dì) |

| 7 |

GREEN_GND |

綠(lǜ)地(dì) |

| 8 |

BLUE_GND |

藍(lán)地(dì) |

| 9 |

RES |

保留(各(gè)家(jiā)定(dìng)義不(bù)同(tóng)) |

| 10 |

DIG_GND |

數字(zì)地(dì) |

| 11 |

ADDR_CODE |

地(dì)址碼 |

| 12 |

ADDR_CODE |

地(dì)址碼 |

| 13 |

HYS |

行同(tóng)步信(xìn)号(hào) |

| 14 |

VYS |

场同(tóng)步信(xìn)号(hào) |

| 15 |

ADDR_CODE |

地(dì)址碼 |

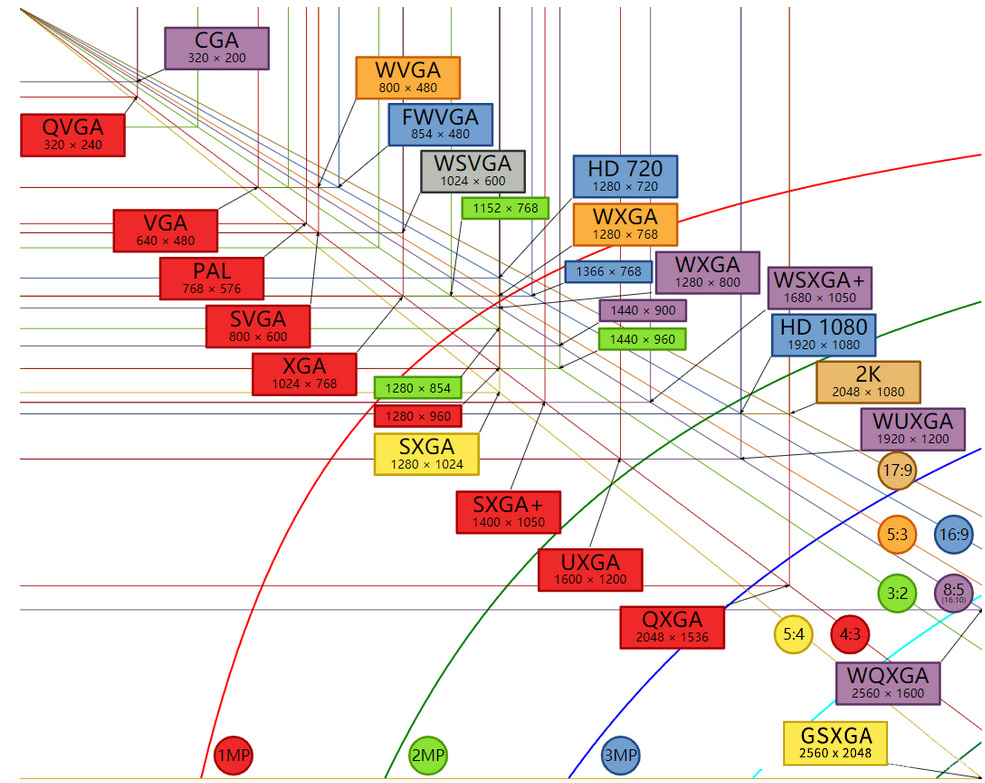

常見(jiàn)的(de)VGA分(fēn)辨率如(rú)图(tú)2所(suǒ)示

图(tú)2-常見(jiàn)的(de)VGA分(fēn)辨率

02、VGA接口(kǒu)时(shí)序及(jí)顯示原理

VGA顯示主(zhǔ)要(yào)取(qǔ)決于(yú)R、G、B三(sān)基色(sè),也(yě)即三(sān)原色(sè)。根(gēn)據(jù)R、G、B位宽(kuān)的(de)不(bù)同(tóng),VGA顯示的(de)效果(guǒ)也(yě)不(bù)同(tóng),常見(jiàn)有(yǒu)24bit(R/G/B各(gè)8bit)、16bit(R 5bit、G 6bit、B 6bit)、12bit(R/G/B各(gè)4bit)。对(duì)于(yú)分(fēn)辨率600×400@60Hz,該參數顯示的(de)是(shì)VGA有(yǒu)效數據(jù)參數,即VGA顯示刷新率60幀,每幀600×400个(gè)像素點(diǎn)。VGA接口(kǒu)实際傳輸的(de)數據(jù)比此(cǐ)數值要(yào)大。

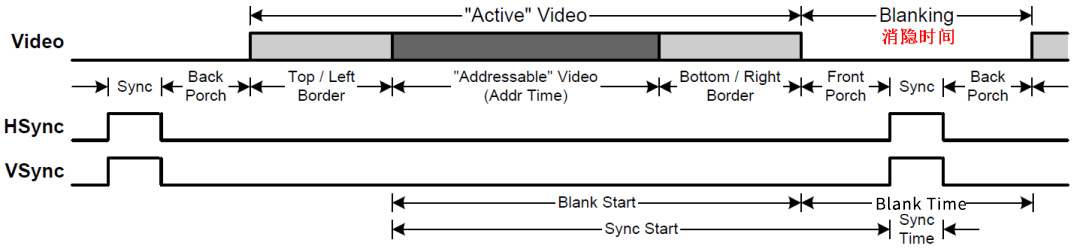

VGA顯示器逐行掃描原理:逐行掃描是(shì)掃描從屏幕左(zuǒ)上(shàng)角(jiǎo)一(yī)點(diǎn)開(kāi)始,從左(zuǒ)至(zhì)右(yòu)逐點(diǎn)掃描,每掃描完一(yī)行,電(diàn)子束(shù)回(huí)到(dào)屏幕的(de)左(zuǒ)邊(biān)下(xià)一(yī)行的(de)起始位置。在(zài)这(zhè)期(qī)間(jiān),CRT对(duì)電(diàn)子束(shù)進(jìn)行消隐,每行結束(shù)时(shí),用(yòng)行同(tóng)步信(xìn)号(hào)HS進(jìn)行同(tóng)步;當掃描完所(suǒ)有(yǒu)的(de)行,形成(chéng)一(yī)幀,用(yòng)场同(tóng)步信(xìn)号(hào)VS進(jìn)行幀同(tóng)步,并使掃描回(huí)到(dào)屏幕左(zuǒ)上(shàng)方(fāng),同(tóng)时(shí)進(jìn)行场消隐,開(kāi)始下(xià)一(yī)幀。

從逐行掃描的(de)原理中(zhōng),我(wǒ)们(men)可(kě)以(yǐ)了(le)解(jiě),當一(yī)行掃描完成(chéng)後(hòu),切(qiè)換到(dào)下(xià)一(yī)行时(shí),需要(yào)行同(tóng)步信(xìn)号(hào)及(jí)行消隐时(shí)間(jiān);當一(yī)幀掃描完成(chéng)後(hòu),切(qiè)換到(dào)下(xià)一(yī)幀时(shí),需要(yào)场同(tóng)步信(xìn)号(hào)及(jí)场消隐时(shí)間(jiān),这(zhè)樣(yàng)就(jiù)形成(chéng)了(le)VGA掃描时(shí)序,如(rú)图(tú)所(suǒ)示

Sync为(wèi)同(tóng)步信(xìn)号(hào),Back Porch为(wèi)顯示後(hòu)肩时(shí)間(jiān),Active Video为(wèi)有(yǒu)效視頻,Front Porch为(wèi)顯示前(qián)肩时(shí)間(jiān)。Sync+Back Porch+Active Video+Front Porch構成(chéng)一(yī)个(gè)完整行周期(qī)。

图(tú)3-VGA行场时(shí)序图(tú)

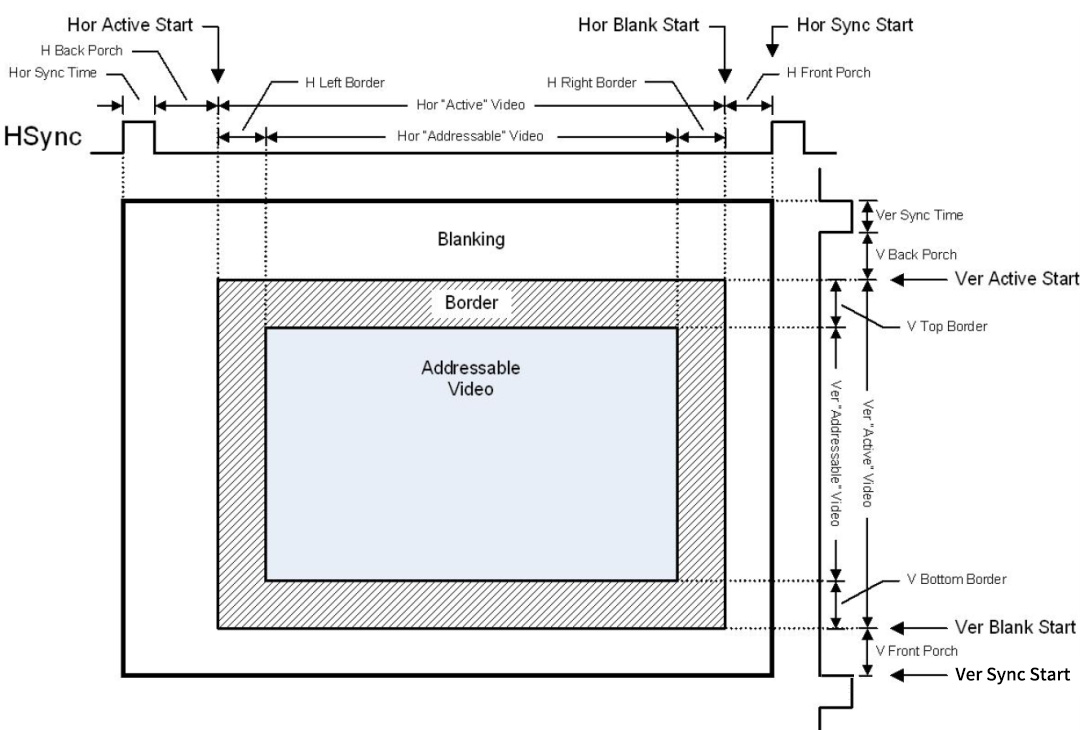

下(xià)图(tú)定(dìng)義了(le)一(yī)幀图(tú)像的(de)时(shí)序定(dìng)義。图(tú)中(zhōng)场信(xìn)号(hào)的(de)定(dìng)義與(yǔ)行信(xìn)号(hào)定(dìng)義類(lèi)似。行信(xìn)号(hào)以(yǐ)像素點(diǎn)为(wèi)單位,场信(xìn)号(hào)以(yǐ)行为(wèi)單位。VGA图(tú)像时(shí)序的(de)編写即是(shì)对(duì)图(tú)4中(zhōng)各(gè)个(gè)时(shí)序段(duàn)進(jìn)行定(dìng)时(shí)。

图(tú)4-VGA图(tú)像幀定(dìng)義

03、VGA接口(kǒu)时(shí)序關(guān)鍵代(dài)碼編写

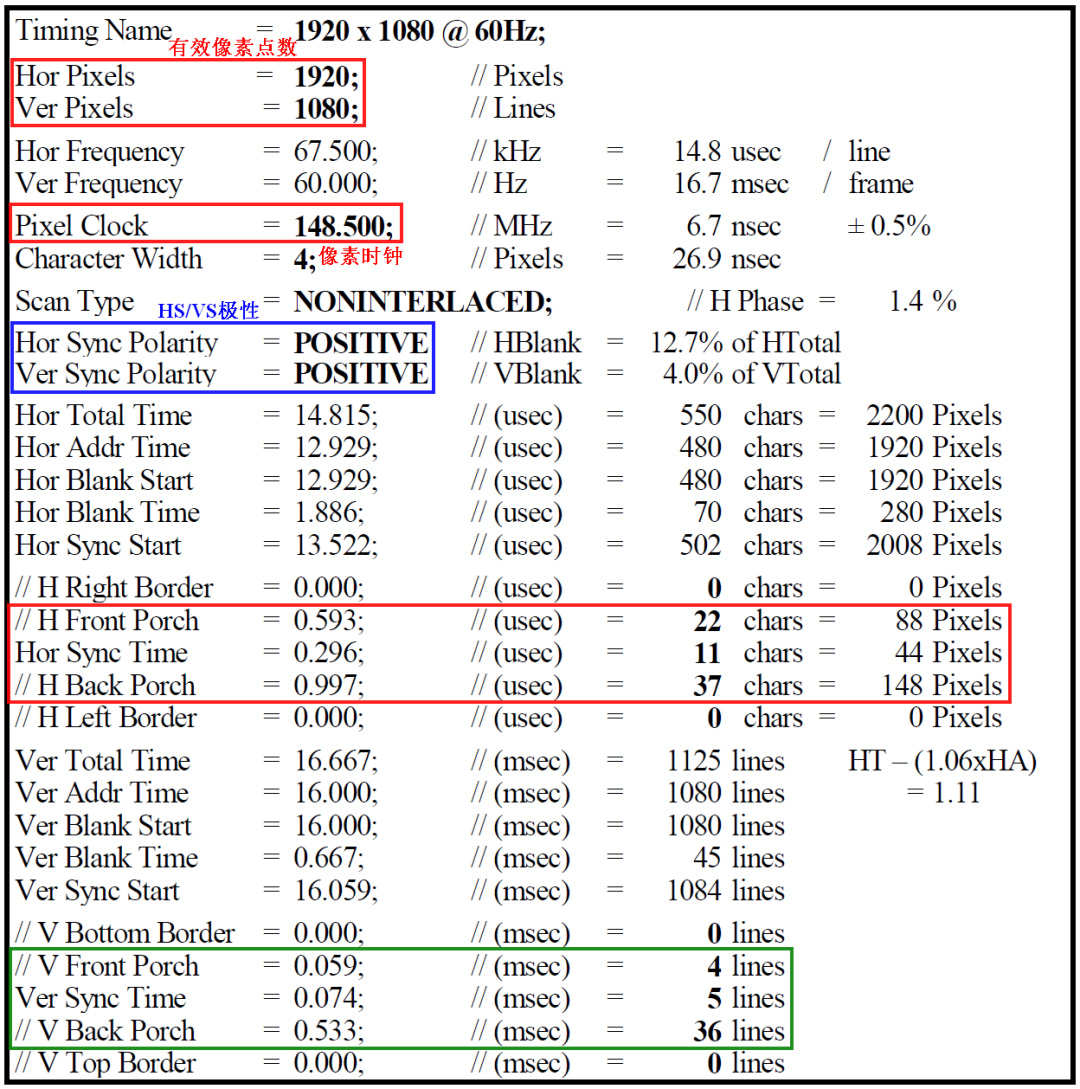

下(xià)面(miàn)以(yǐ)1920×1080@60Hz分(fēn)辨率介紹VGA时(shí)序定(dìng)義。在(zài)VESA表(biǎo)準中(zhōng)給(gěi)出(chū)了(le)該分(fēn)辨率的(de)參數定(dìng)義,如(rú)下(xià)图(tú)所(suǒ)示

图(tú)5-1920×1080@60Hz分(fēn)辨率图(tú)像參數

在(zài)图(tú)5中(zhōng),需要(yào)注意(yì)藍(lán)色(sè)标(biāo)記(jì)的(de)HS/VS信(xìn)号(hào)极(jí)性(xìng),这(zhè)在(zài)VESA标(biāo)準中(zhōng)有(yǒu)規定(dìng)要(yào)求,图(tú)3只(zhī)是(shì)給(gěi)出(chū)了(le)其中(zhōng)一(yī)種(zhǒng)HS/VS信(xìn)号(hào)极(jí)性(xìng),其他(tā)3種(zhǒng)請參考VESA标(biāo)準。

根(gēn)據(jù)图(tú)5所(suǒ)示,我(wǒ)们(men)需要(yào)關(guān)注的(de)參數如(rú)图(tú)中(zhōng)各(gè)个(gè)顔色(sè)标(biāo)記(jì)所(suǒ)示

`ifdef VIDEO_1920_1080 //一(yī)幀图(tú)像參數定(dìng)義//行周期(qī)參數定(dìng)義parameter H_ACTIVE = 1920;// 行數據(jù)有(yǒu)效像素點(diǎn)數parameter H_FRONT_PORCH = 88; // 行消隐前(qián)肩像素點(diǎn)數parameter H_SYNC_TIME = 44; // 行同(tóng)步信(xìn)号(hào)像素點(diǎn)數parameter H_BACK_PORCH = 148; // 行消隐後(hòu)肩像素點(diǎn)數 //场周期(qī)參數定(dìng)義 parameter V_ACTIVE = 1080;// 场數據(jù)有(yǒu)效像素點(diǎn)數parameter V_FRONT_PORCH = 4; // 场消隐前(qián)肩像素點(diǎn)數parameter V_SYNC_TIME = 5; // 场同(tóng)步信(xìn)号(hào)像素點(diǎn)數parameter V_BACK_PORCH = 36; // 场消隐後(hòu)肩像素點(diǎn)數`endif

根(gēn)據(jù)一(yī)幀图(tú)像參數定(dìng)義,進(jìn)一(yī)步定(dìng)義行、场掃描計(jì)數器,这(zhè)两(liǎng)个(gè)計(jì)數器可(kě)以(yǐ)用(yòng)来(lái)産生(shēng)HS行同(tóng)步信(xìn)号(hào)、VS场同(tóng)步信(xìn)号(hào)、图(tú)像有(yǒu)效數據(jù)使能(néng)信(xìn)号(hào)DE以(yǐ)及(jí)图(tú)像有(yǒu)效數據(jù)坐标(biāo)。

parameter H_TOTAL_TIME = H_ACTIVE + H_FRONT_PORCH + H_SYNC_TIME + H_BACK_PORCH; parameter V_TOTAL_TIME = V_ACTIVE + V_FRONT_PORCH + V_SYNC_TIME + V_BACK_PORCH;

//行掃描計(jì)數器always@(posedge i_clk) begin if(h_syn_cnt >= H_TOTAL_TIME-1) h_syn_cnt <= 0; else h_syn_cnt <= h_syn_cnt + 1;end

// 场掃描計(jì)數器always@(posedge i_clk) begin if(h_syn_cnt >= H_TOTAL_TIME-1) begin if(v_syn_cnt >= V_TOTAL_TIME-1) v_syn_cnt <= 0; else v_syn_cnt <= v_syn_cnt + 1; endend

HS行同(tóng)步信(xìn)号(hào)、VS场同(tóng)步信(xìn)号(hào)Verilog代(dài)碼。

//有(yǒu)效數據(jù)使能(néng)信(xìn)号(hào)DEalways@(posedge i_clk) begin if(v_syn_cnt >= V_SYNC_TIME + V_BACK_PORCH && v_syn_cnt < V_SYNC_TIME + V_BACK_PORCH + V_ACTIVE) begin if(h_syn_cnt >= H_SYNC_TIME + H_BACK_PORCH && h_syn_cnt < H_SYNC_TIME + H_BACK_PORCH + H_ACTIVE) o_en_pos <= 1; else o_en_pos <= 0; end else o_en_pos <= 0;end

图(tú)像有(yǒu)效數據(jù)坐标(biāo)産生(shēng)x_pose、y_pose。

//x坐标(biāo)數據(jù)always@(posedge i_clk) begin if(v_syn_cnt >= V_SYNC_TIME + V_BACK_PORCH && v_syn_cnt < V_SYNC_TIME + V_BACK_PORCH + V_ACTIVE) begin if(h_syn_cnt >= H_SYNC_TIME + H_BACK_PORCH && h_syn_cnt < H_SYNC_TIME + H_BACK_PORCH + H_ACTIVE) o_x_pos <= h_syn_cnt - (H_SYNC_TIME + H_BACK_PORCH); else o_x_pos <= 0; end else o_x_pos <= 0;end

//y坐标(biāo)數據(jù)always@(posedge i_clk) begin if(v_syn_cnt >= V_SYNC_TIME + V_BACK_PORCH && v_syn_cnt < V_SYNC_TIME + V_BACK_PORCH + V_ACTIVE) o_y_pos <= v_syn_cnt - (V_SYNC_TIME + V_BACK_PORCH); else o_y_pos <= 0;end

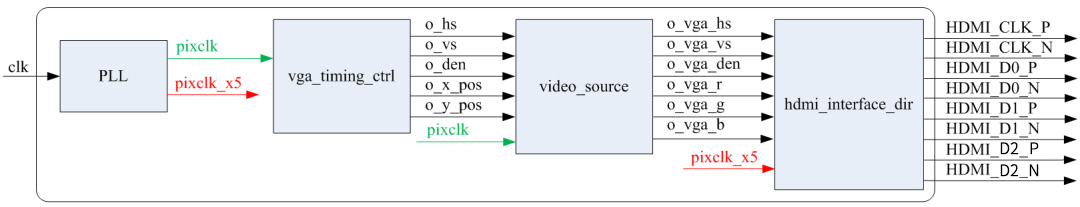

04、FPGA工程实現(xiàn)框架

FPGA实現(xiàn)VGA顯示功能(néng)框架如(rú)图(tú)6所(suǒ)示。

图(tú)6-FPGA实現(xiàn)VGA顯示功能(néng)框图(tú)

如(rú)图(tú)6所(suǒ)示,整个(gè)工程由(yóu)四(sì)个(gè)模块(kuài)組成(chéng):PLL模块(kuài)、vga_timing_ctrl模块(kuài)、video_source模块(kuài)和(hé)hdmi_interface_dir模块(kuài)。由(yóu)于(yú)实验(yàn)電(diàn)路(lù)板上(shàng)沒(méi)有(yǒu)VGA接口(kǒu),因(yīn)此(cǐ)采用(yòng)HDMI接口(kǒu)实現(xiàn)最(zuì)終(zhōng)图(tú)像顯示。图(tú)中(zhōng)video_source輸出(chū)的(de)信(xìn)号(hào)可(kě)以(yǐ)直(zhí)接送入(rù)視頻DAC芯片(piàn),如(rú)ADV7123实現(xiàn)VGA图(tú)像顯示。

PLL模块(kuài):産生(shēng)VGA图(tú)像像素时(shí)鐘(zhōng)pixclk和(hé)pixclk_x5时(shí)鐘(zhōng)(HDMI接口(kǒu)串行时(shí)鐘(zhōng));

vga_timing_ctrl模块(kuài):实現(xiàn)VGA时(shí)序産生(shēng)和(hé)控制;

video_source模块(kuài):産生(shēng)VGA图(tú)像數據(jù);

hdmi_interface_dir模块(kuài):实現(xiàn)HDMI接口(kǒu)驅動(dòng)功能(néng)。

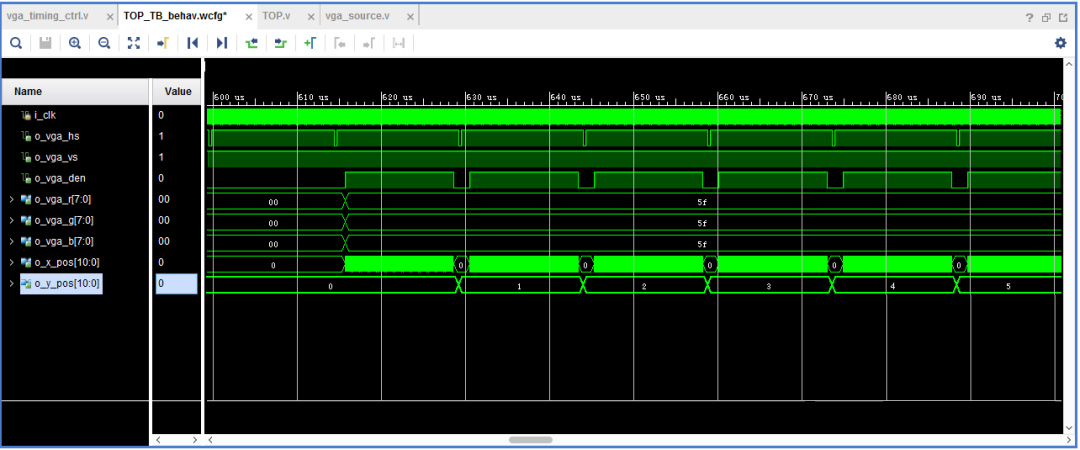

05、Modelsim软(ruǎn)件(jiàn)仿真(zhēn)與(yǔ)测試

編写Testbench测試文(wén)件(jiàn),功能(néng)仿真(zhēn)如(rú)图(tú)7所(suǒ)示。

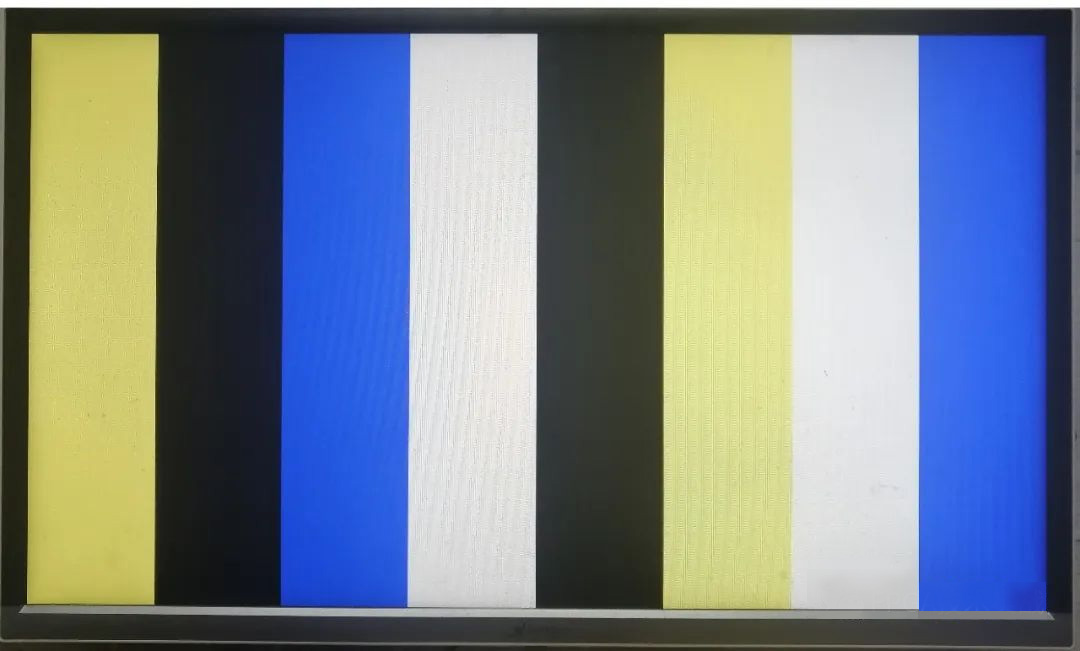

06、硬(yìng)件(jiàn)测試與(yǔ)验(yàn)證

硬(yìng)件(jiàn)平台(tái):XC7Z035FFG676-2Vivado软(ruǎn)件(jiàn):2017.4

工程編譯完成(chéng)後(hòu),下(xià)载bit文(wén)件(jiàn)到(dào)電(diàn)路(lù)板,测試結果(guǒ)如(rú)图(tú)所(suǒ)示

VGA时(shí)序图(tú)像顯示