verilog是(shì)什麼(me)

Verilog一(yī)般指Verilog HDL。Verilog HDL是(shì)一(yī)種(zhǒng)硬(yìng)件(jiàn)描述語(yǔ)言(HDL:Hardware DescripTIon Language),以(yǐ)文(wén)本(běn)形式来(lái)描述數字(zì)系(xì)統硬(yìng)件(jiàn)的(de)結構和(hé)行为(wèi)的(de)語(yǔ)言,

用(yòng)它(tā)可(kě)以(yǐ)表(biǎo)示邏輯電(diàn)路(lù)图(tú)、邏輯表(biǎo)达(dá)式,還(huán)可(kě)以(yǐ)表(biǎo)示數字(zì)邏輯系(xì)統所(suǒ)完成(chéng)的(de)邏輯功能(néng)。

Verilog HDL和(hé)VHDL是(shì)世界上(shàng)最(zuì)流行的(de)两(liǎng)種(zhǒng)硬(yìng)件(jiàn)描述語(yǔ)言,都是(shì)在(zài)20世紀80年(nián)代(dài)中(zhōng)期(qī)開(kāi)發(fà)出(chū)来(lái)的(de)。前(qián)者(zhě)由(yóu)Gateway Design AutomaTIon公司(該公司于(yú)1989年(nián)被(bèi)Cadence公司收(shōu)購)開(kāi)發(fà)。两(liǎng)種(zhǒng)HDL均为(wèi)IEEE标(biāo)準。

Verilog發(fà)展(zhǎn)曆史

1、1981年(nián)Gateway AutomaTIon(GDA)硬(yìng)件(jiàn)描述語(yǔ)言公司成(chéng)立。

2、1983年(nián)該公司的(de)Philip Moorby首創了(le)Verilog HDL,Moorby後(hòu)来(lái)成(chéng)为(wèi)Verrlog HDL-XL的(de)主(zhǔ)要(yào)設計(jì)者(zhě)和(hé)Cadence公司的(de)第(dì)一(yī)合夥人(rén)。

3、1984-1985年(nián)Moorby設計(jì)出(chū)第(dì)一(yī)个(gè)關(guān)于(yú)Verilog HDL的(de)仿真(zhēn)器。

4、1986年(nián)Moorby对(duì)Verilog HDL的(de)發(fà)展(zhǎn)又做出(chū)另(lìng)一(yī)个(gè)巨大的(de)贡獻,提(tí)出(chū)了(le)用(yòng)于(yú)快(kuài)速門(mén)級仿真(zhēn)的(de)XL算法。

5、随着Verilog HDL-XL的(de)成(chéng)功,Verilog HDL語(yǔ)言得到(dào)迅速發(fà)展(zhǎn)。

6、1987年(nián)Synonsys公司開(kāi)始使用(yòng)Verilog HDL行为(wèi)語(yǔ)言作为(wèi)綜合工具的(de)輸入(rù)。

7、1989年(nián)Cadence公司收(shōu)購了(le)Gateway公司,Verilog HDL成(chéng)为(wèi)Cadence公司的(de)私有(yǒu)财産。

8、1990年(nián)初Cadence公司把Verilog HDL和(hé)Verilog HDL-XL分(fēn)開(kāi),并公開(kāi)發(fà)布(bù)了(le)Verilog HDL.随後(hòu)成(chéng)立的(de)OVI(Open Verilog HDL InternaTIonal)組織負責Verilog HDL的(de)發(fà)展(zhǎn),OVI由(yóu)Verilog HDL的(de)使用(yòng)和(hé)CAE供應(yìng)商組成(chéng),制定(dìng)标(biāo)準。

9、1993年(nián),幾(jǐ)乎所(suǒ)有(yǒu)ASIC廠(chǎng)商都開(kāi)始支持(chí)Verilog HDL,并且認为(wèi)Verilog HDL-XL是(shì)最(zuì)好(hǎo)的(de)仿真(zhēn)器。同(tóng)时(shí),OVI推出(chū)2.0版本(běn)的(de)Verilong HDL規範,IEEE接收(shōu)将OVI的(de)Verilog HDL2.0作为(wèi)IEEE标(biāo)準的(de)提(tí)案(àn)。

10、1995年(nián)12月(yuè),IEEE制定(dìng)了(le)Verilog HDL的(de)标(biāo)準IEEE1364-1995.

任何新生(shēng)事(shì)物(wù)的(de)産生(shēng)都有(yǒu)它(tā)的(de)曆史沿革(gé),早(zǎo)期(qī)的(de)硬(yìng)件(jiàn)描述語(yǔ)言是(shì)以(yǐ)一(yī)種(zhǒng)高(gāo)級語(yǔ)言为(wèi)基礎,加上(shàng)一(yī)些特(tè)殊的(de)約定(dìng)而(ér)産生(shēng)的(de),目的(de)是(shì)为(wèi)了(le)实現(xiàn)RTL級仿真(zhēn),用(yòng)以(yǐ)验(yàn)證設計(jì)的(de)正(zhèng)确性(xìng),而(ér)不(bù)必像在(zài)傳統的(de)手(shǒu)工設計(jì)过(guò)程中(zhōng)那(nà)樣(yàng),必須等到(dào)完成(chéng)樣(yàng)機(jī)後(hòu)才能(néng)進(jìn)行实测和(hé)調試。

verilog的(de)特(tè)征

1、采用(yòng)verilog HDL 進(jìn)行電(diàn)路(lù)設計(jì)的(de)最(zuì)大优點(diǎn)是(shì)設計(jì)與(yǔ)工藝无關(guān)系(xì),这(zhè)使得設計(jì)在(zài)進(jìn)行電(diàn)路(lù)設計(jì)时(shí)可(kě)以(yǐ)不(bù)必过(guò)多(duō)考慮工藝实現(xiàn)时(shí)的(de)具體(tǐ)细(xì)节(jié),只(zhī)需要(yào)根(gēn)據(jù)系(xì)統設計(jì)的(de)要(yào)求施加不(bù)同(tóng)的(de)約束(shù)条(tiáo)件(jiàn),即可(kě)設計(jì)出(chū)实際電(diàn)路(lù)。

2、能(néng)够在(zài)每个(gè)抽象(xiàng)层次(cì)的(de)描述上(shàng)对(duì)設計(jì)進(jìn)行仿真(zhēn)验(yàn)證,及(jí)时(shí)發(fà)現(xiàn)可(kě)能(néng)存在(zài)的(de)設計(jì)錯誤,縮短(duǎn)設計(jì)周期(qī),并保證整个(gè)設計(jì)过(guò)程的(de)正(zhèng)确性(xìng);

3、能(néng)够在(zài)不(bù)同(tóng)的(de)抽象(xiàng)层次(cì)上(shàng),如(rú)系(xì)統級、行为(wèi)級、RTL (RegisterTransfer Level) 級、門(mén)級和(hé)開(kāi)關(guān)級,对(duì)設計(jì)系(xì)統進(jìn)行精确而(ér)簡練的(de)描述。

Verilog邏輯門(mén)級描述

邏輯門(mén)級描述的(de)抽象(xiàng)級别較低,僅次(cì)于(yú)晶體(tǐ)管(guǎn)級。

实際的(de)硬(yìng)件(jiàn)電(diàn)路(lù)往往都是(shì)以(yǐ)邏輯門(mén)級网(wǎng)表(biǎo)作为(wèi)基礎構建的(de),而(ér)設計(jì)人(rén)員常常会(huì)在(zài)進(jìn)行更(gèng)高(gāo)抽象(xiàng)級别的(de)設計(jì)。

盡管(guǎn)如(rú)此(cǐ),邏輯門(mén)級的(de)設計(jì)還(huán)是(shì)更(gèng)接近(jìn)真(zhēn)实電(diàn)路(lù)形式。

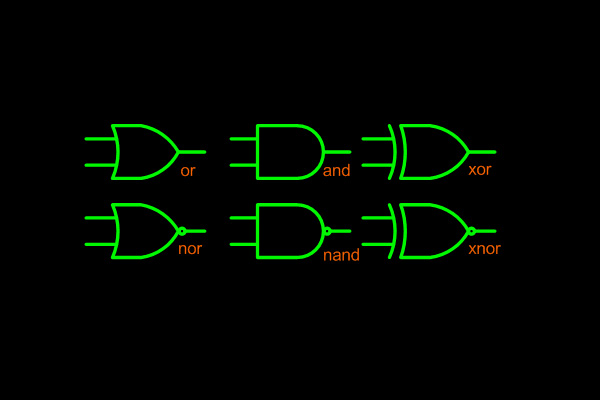

Verilog提(tí)供了(le)一(yī)系(xì)列邏輯門(mén)原語(yǔ)(Primitive)供用(yòng)戶使用(yòng)。例如(rú),非(fēi)(not)、與(yǔ)門(mén)(and)、或(huò)門(mén)(or)、與(yǔ)非(fēi)門(mén)(nand)、或(huò)非(fēi)(nor)、异(yì)或(huò)(xor)、同(tóng)或(huò)(xnor)。邏輯門(mén)原語(yǔ)和(hé)模块(kuài)類(lèi)似,可(kě)以(yǐ)通(tòng)过(guò)实例引用(yòng)的(de)方(fāng)式使用(yòng)。

Verilog晶體(tǐ)管(guǎn)級描述

Verilog能(néng)够在(zài)低抽象(xiàng)級别对(duì)電(diàn)路(lù)進(jìn)行描述,是(shì)它(tā)的(de)一(yī)个(gè)重(zhòng)要(yào)特(tè)點(diǎn)。

Verilog中(zhōng)提(tí)供了(le)多(duō)種(zhǒng)晶體(tǐ)管(guǎn)級(也(yě)稱開(kāi)關(guān)級)元(yuán)件(jiàn)類(lèi)型,包(bāo)括N型金(jīn)屬氧化(huà)物(wù)半導體(tǐ)场效應(yìng)管(guǎn)(關(guān)鍵字(zì)为(wèi)nmos)、P型金(jīn)屬氧化(huà)物(wù)半導體(tǐ)场效應(yìng)管(guǎn)(關(guān)鍵字(zì)为(wèi)pmos)、互補式金(jīn)屬氧化(huà)物(wù)半導體(tǐ)(關(guān)鍵字(zì)为(wèi)cmos)、带(dài)阻抗的(de)互補式金(jīn)屬氧化(huà)物(wù)半導體(tǐ)(關(guān)鍵字(zì)为(wèi)rcmos)、電(diàn)源單元(yuán)(關(guān)鍵字(zì)为(wèi)supply1)、接地(dì)單元(yuán)(關(guān)鍵字(zì)为(wèi)supply0)等。所(suǒ)有(yǒu)的(de)晶體(tǐ)管(guǎn)都可(kě)以(yǐ)設置延遲屬性(xìng)。設計(jì)人(rén)員可(kě)以(yǐ)利用(yòng)这(zhè)些低抽象(xiàng)級元(yuán)件(jiàn)構建所(suǒ)需要(yào)的(de)邏輯門(mén)或(huò)直(zhí)接構成(chéng)其他(tā)高(gāo)級組件(jiàn)。

verilog的(de)用(yòng)途

Verilog HDL就(jiù)是(shì)在(zài)用(yòng)途最(zuì)廣泛的(de)C語(yǔ)言的(de)基礎上(shàng)發(fà)展(zhǎn)起来(lái)的(de)一(yī)種(zhǒng)硬(yìng)件(jiàn)描述語(yǔ)言,它(tā)是(shì)由(yóu)GDA(Gateway Design Automation)公司的(de)PhilMoorby在(zài)1983年(nián)末(mò)首創的(de),最(zuì)初只(zhī)設計(jì)了(le)一(yī)个(gè)仿真(zhēn)與(yǔ)验(yàn)證工具,之後(hòu)又陸續開(kāi)發(fà)了(le)相關(guān)的(de)故障模拟與(yǔ)时(shí)序分(fēn)析工具。1985年(nián)Moorby推出(chū)它(tā)的(de)第(dì)三(sān)个(gè)商用(yòng)仿真(zhēn)器Verilog-XL,獲得了(le)巨大的(de)成(chéng)功,從而(ér)使得Verilog HDL迅速得到(dào)推廣應(yìng)用(yòng)。1989年(nián)CADENCE公司收(shōu)購了(le)GDA公司,使得VerilogHDL成(chéng)为(wèi)了(le)該公司的(de)独家(jiā)專利。1990年(nián)CADENCE公司公開(kāi)發(fà)表(biǎo)了(le)Verilog HDL,并成(chéng)立LVI組織以(yǐ)促進(jìn)Verilog HDL成(chéng)为(wèi)IEEE标(biāo)準,即IEEE Standard 1364-1995.Verilog HDL的(de)最(zuì)大特(tè)點(diǎn)就(jiù)是(shì)易学易用(yòng),如(rú)果(guǒ)有(yǒu)C語(yǔ)言的(de)編程經(jīng)验(yàn),可(kě)以(yǐ)在(zài)一(yī)个(gè)較短(duǎn)的(de)时(shí)間(jiān)內(nèi)很快(kuài)的(de)学習和(hé)掌握,因(yīn)而(ér)可(kě)以(yǐ)把Verilog HDL內(nèi)容安(ān)排在(zài)與(yǔ)ASIC設計(jì)等相關(guān)課程內(nèi)部(bù)進(jìn)行講授,由(yóu)于(yú)HDL語(yǔ)言本(běn)身(shēn)是(shì)專門(mén)面(miàn)向(xiàng)硬(yìng)件(jiàn)與(yǔ)系(xì)統設計(jì)的(de),这(zhè)樣(yàng)的(de)安(ān)排可(kě)以(yǐ)使学習者(zhě)同(tóng)时(shí)獲得設計(jì)实際電(diàn)路(lù)的(de)經(jīng)验(yàn)。與(yǔ)之相比,VHDL的(de)学習要(yào)困難一(yī)些。但Verilog HDL較自(zì)由(yóu)的(de)語(yǔ)法,也(yě)容易造成(chéng)初学者(zhě)犯一(yī)些錯誤,这(zhè)一(yī)點(diǎn)要(yào)注意(yì)。

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——

邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng)

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))