1、 項目背景

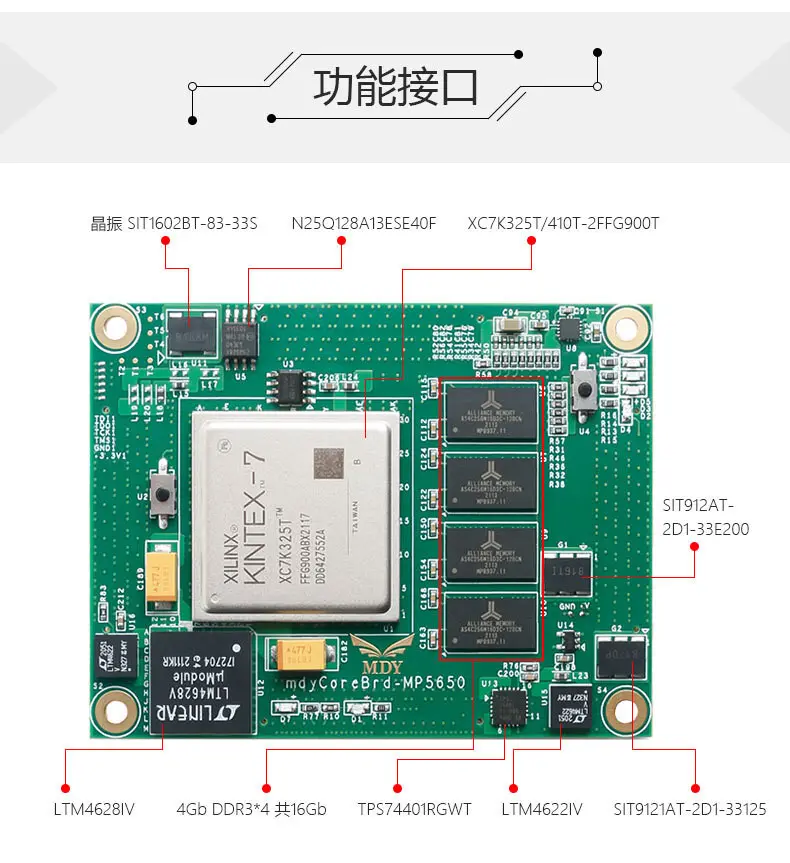

明(míng)德揚(MDY)为(wèi)某研究所(suǒ)研制的(de)視頻接口(kǒu)轉(zhuǎn)換模块(kuài),該模块(kuài)将HDMI視頻轉(zhuǎn)成(chéng)LVDS7:1視頻。視頻輸入(rù)接口(kǒu)采用(yòng)的(de)是(shì)HDMI 4K輸入(rù),基于(yú)Xilinx K7325t的(de)高(gāo)速收(shōu)發(fà)器,特(tè)點(diǎn)是(shì)无需外(wài)圍HDMI接收(shōu)芯片(piàn),大大簡化(huà)了(le)硬(yìng)件(jiàn)設計(jì)。該視頻接口(kǒu)轉(zhuǎn)換模块(kuài)如(rú)图(tú)1所(suǒ)示,其中(zhōng)k7核心(xīn)板型号(hào)为(wèi)MP5650,底板和(hé)核心(xīn)板均为(wèi)明(míng)德揚自(zì)研産品。

本(běn)文(wén)簡單介紹了(le)Xilinx官方(fāng)的(de)HDMI例程的(de)建立步驟。

图(tú)1視頻接口(kǒu)轉(zhuǎn)換模块(kuài)

图(tú)2 MP5650核心(xīn)板

2、工具

Vivado 2022.1;

Vitis 2022.1;

HDMI License。

3、操作步驟

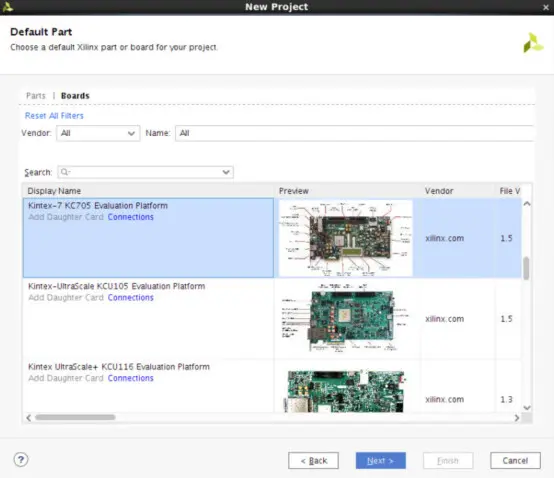

(1)新建一(yī)个(gè)vivado工程,平台(tái)選擇KC705。

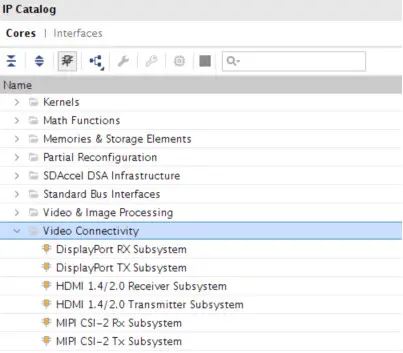

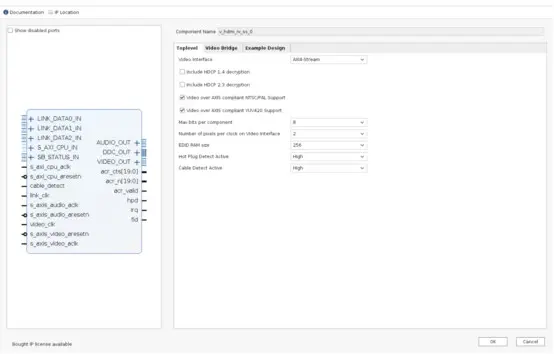

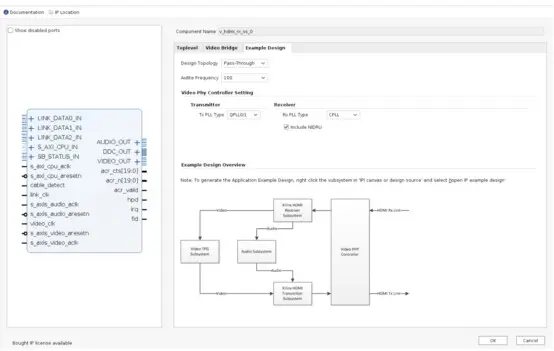

(2)選擇HDMI 1.4/2.0 Receiver Subsystem IP核,按下(xià)图(tú)進(jìn)行IP核的(de)配置。

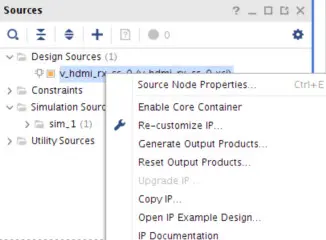

(3)配置完後(hòu),并自(zì)動(dòng)産生(shēng)IP相關(guān)文(wén)件(jiàn),在(zài)IP核上(shàng)右(yòu)鍵選擇Open IP Example Design,選擇例程的(de)存儲路(lù)徑,點(diǎn)擊OK。

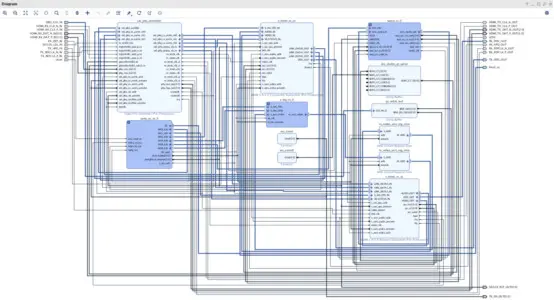

(4)软(ruǎn)件(jiàn)会(huì)自(zì)動(dòng)生(shēng)成(chéng)一(yī)个(gè)例程,待例程生(shēng)成(chéng)結束(shù),進(jìn)行Synthesis、 Implementation和(hé) GenerateBitstream流程生(shēng)成(chéng)bit文(wén)件(jiàn)。

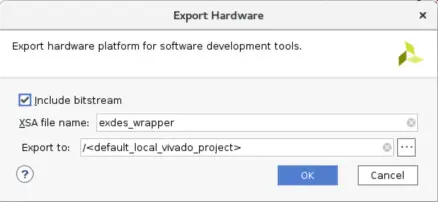

(5)導出(chū)硬(yìng)件(jiàn)底层,建立vitis工程,選擇File → Export → Export Hardware。

(6)建立一(yī)个(gè)文(wén)件(jiàn)夾,用(yòng)来(lái)存放(fàng)Vitis工程,啟動(dòng)Vitis,選擇Tools → Launch Vitis IDE。

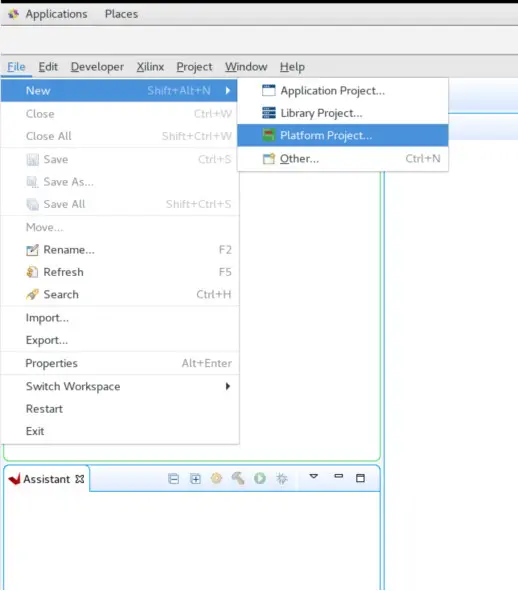

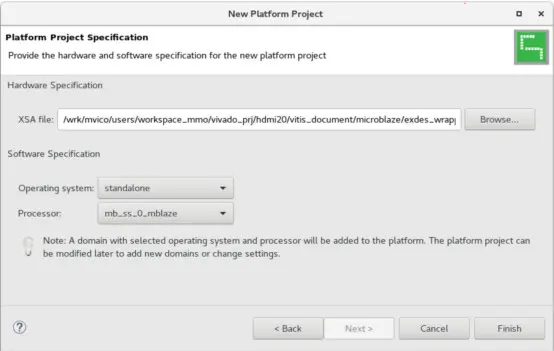

(7)打(dǎ)開(kāi)Vitis环(huán)境,建立平台(tái)工程,選擇File → New → Platform Project。

(8)選擇vivado生(shēng)成(chéng)的(de)exdes_wrapper.xsa文(wén)件(jiàn),點(diǎn)擊Finish。

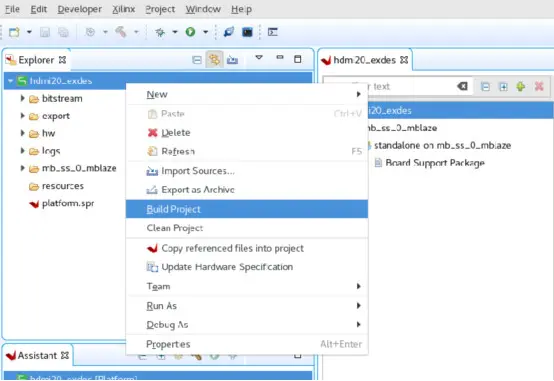

(9)右(yòu)鍵生(shēng)成(chéng)的(de)硬(yìng)件(jiàn)平台(tái),選擇Build Project。

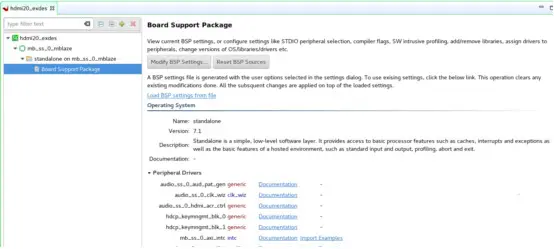

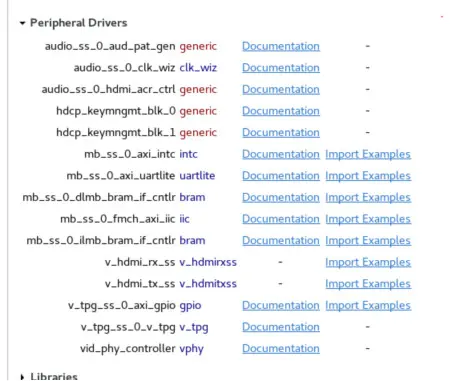

(10)在(zài)platform.spr页(yè)面(miàn),選擇Board Support Package,展(zhǎn)開(kāi)Peripheral Drivers。

(11)在(zài)Peripheral Drivers下(xià),找(zhǎo)到(dào)v_hdmi_rx_ss或(huò)者(zhě)v_hdmi_tx_ss,點(diǎn)擊Import Examples。

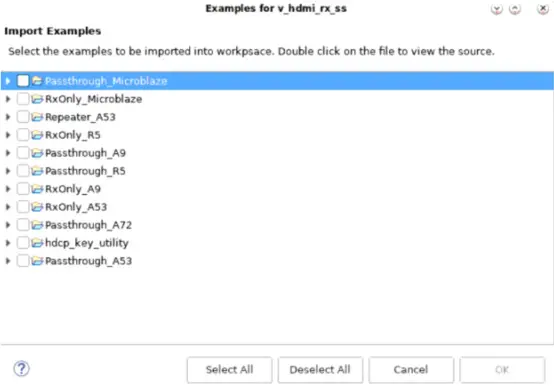

(12)在(zài)Import Examples選項中(zhōng),選擇一(yī)个(gè)應(yìng)用(yòng)工程,Microblaze对(duì)應(yìng)的(de)工程有(yǒu)Passthrough_Microblaze、Rxonly_Microblaze,Txonly_Microblaze。

(13)Build當前(qián)應(yìng)用(yòng)工程,得到(dào).elf文(wén)件(jiàn)。

温(wēn)馨提(tí)示:明(míng)德揚擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 前(qián)端模拟采集、射頻、電(diàn)荷靈敏前(qián)置放(fàng)大器

需要(yào)了(le)解(jiě)相關(guān)信(xìn)息可(kě)以(yǐ)聯系(xì):吴老(lǎo)师(shī)18022857217(微信(xìn)同(tóng)号(hào))