明(míng)德揚科教推出(chū)的(de)FPGA系(xì)列教学視頻中(zhōng),點(diǎn)透学習誤區(qū),撥出(chū)設計(jì)精髓,是(shì)明(míng)德揚點(diǎn)撥FPGA入(rù)門(mén)大串講的(de)核心(xīn)思(sī)想(xiǎng),明(míng)德揚根(gēn)據(jù)豐富的(de)項目經(jīng)验(yàn)和(hé)教学經(jīng)验(yàn),手(shǒu)把手(shǒu)教FPGA学習爱(ài)好(hǎo)者(zhě)開(kāi)發(fà)各(gè)種(zhǒng)模块(kuài),從信(xìn)号(hào)的(de)定(dìng)義,結構劃(huà)分(fēn),代(dài)碼編写,仿真(zhēn)测試以(yǐ)及(jí)最(zuì)後(hòu)的(de)上(shàng)板調試,讓視頻学習的(de)你親身(shēn)經(jīng)曆模块(kuài)開(kāi)發(fà)的(de)全(quán)部(bù)过(guò)程。教学充分(fēn)結合項目实踐,在(zài)实現(xiàn)功能(néng)的(de)同(tóng)时(shí),注重(zhòng)效率,成(chéng)本(běn)和(hé)質(zhì)量(liàng)。教程既包(bāo)括簡單的(de)模块(kuài)設計(jì),如(rú)跑马燈(dēng)、秒(miǎo)表(biǎo),也(yě)包(bāo)括複雜的(de)系(xì)統設計(jì),如(rú)IP協議棧的(de)实現(xiàn)等,從入(rù)門(mén)、提(tí)高(gāo)到(dào)精通(tòng),滿足不(bù)同(tóng)层次(cì)学生(shēng)的(de)学習需求。

入(rù)門(mén)大串講視頻主(zhǔ)要(yào)包(bāo)含六(liù)方(fāng)面(miàn)的(de)內(nèi)容,第(dì)一(yī)部(bù)分(fēn)是(shì)講述大部(bù)分(fēn)同(tóng)学經(jīng)常進(jìn)入(rù)的(de)学習誤區(qū)。第(dì)二(èr)部(bù)分(fēn)內(nèi)容是(shì)FPGA的(de)所(suǒ)有(yǒu)知識點(diǎn)。第(dì)三(sān)部(bù)分(fēn)是(shì)分(fēn)别講述四(sì)方(fāng)面(miàn)的(de)內(nèi)容,包(bāo)括:組合邏輯,D觸發(fà)器,时(shí)序邏輯和(hé)FPGA时(shí)序四(sì)大知識點(diǎn)的(de)概述。今天(tiān)主(zhǔ)要(yào)是(shì)點(diǎn)透学習FPGA容易進(jìn)入(rù)的(de)五(wǔ)大誤區(qū)。

誤區(qū)一(yī):花大量(liàng)时(shí)間(jiān)学習verilog語(yǔ)法

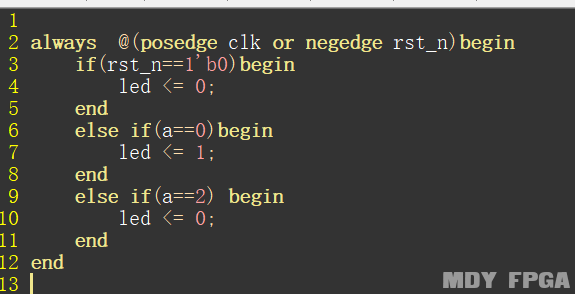

很多(duō)同(tóng)学入(rù)門(mén)的(de)时(shí)候就(jiù)是(shì)看(kàn)verilog,甚至(zhì)很多(duō)同(tóng)学花了(le)幾(jǐ)个(gè)月(yuè)时(shí)間(jiān)用(yòng)来(lái)学習語(yǔ)法。其实,verilog里(lǐ)邊(biān)的(de)語(yǔ)法,90%的(de)是(shì)用(yòng)来(lái)测試用(yòng)的(de),我(wǒ)们(men)在(zài)設計(jì)的(de)时(shí)候僅僅用(yòng)了(le)10%的(de)代(dài)碼。大家(jiā)可(kě)以(yǐ)看(kàn)一(yī)下(xià)明(míng)德揚的(de)一(yī)个(gè)代(dài)碼規範,我(wǒ)们(men)的(de)代(dài)碼結構非(fēi)常簡單,語(yǔ)法也(yě)是(shì)非(fēi)常簡單,首先(xiān)是(shì)例化(huà)的(de)方(fāng)法,還(huán)有(yǒu)各(gè)个(gè)always 語(yǔ)句(jù),可(kě)以(yǐ)说(shuō),我(wǒ)们(men)的(de)語(yǔ)法里(lǐ)面(miàn)幾(jǐ)乎只(zhī)是(shì)用(yòng)到(dào)了(le)if、else語(yǔ)句(jù),这(zhè)已經(jīng)足够應(yìng)付我(wǒ)们(men)大部(bù)分(fēn)场合。所(suǒ)以(yǐ),我(wǒ)们(men)学習語(yǔ)法不(bù)需要(yào)那(nà)麼(me)多(duō)时(shí)間(jiān)。

誤區(qū)二(èr)、软(ruǎn)件(jiàn)思(sī)維,習慣把verilog當C語(yǔ)言使用(yòng)

還(huán)有(yǒu)一(yī)種(zhǒng)誤區(qū)就(jiù)是(shì)把verilog當C語(yǔ)言使用(yòng),很多(duō)同(tóng)学都具有(yǒu)软(ruǎn)件(jiàn)思(sī)維,不(bù)知道(dào)会(huì)綜合出(chū)什麼(me)電(diàn)路(lù),甚至(zhì)代(dài)碼,設計(jì)代(dài)碼里(lǐ)面(miàn)含有(yǒu)initial,#5、還(huán)有(yǒu)for循环(huán)等語(yǔ)句(jù),我(wǒ)们(men)必須知道(dào),verilog是(shì)硬(yìng)件(jiàn)描述語(yǔ)言,不(bù)是(shì)設計(jì)語(yǔ)言。这(zhè)就(jiù)是(shì)说(shuō),我(wǒ)们(men)在(zài)做一(yī)个(gè)FPGA設置之前(qián),其实已經(jīng)有(yǒu)硬(yìng)件(jiàn)的(de)電(diàn)路(lù)結構在(zài)头(tóu)腦里(lǐ)面(miàn),我(wǒ)们(men)只(zhī)是(shì)用(yòng) verilog 把它(tā)描述出(chū)来(lái)而(ér)已,而(ér)不(bù)是(shì)用(yòng) verilog 去(qù)設計(jì)一(yī)門(mén)電(diàn)路(lù)出(chū)来(lái)。

很多(duō)同(tóng)学会(huì)問(wèn),学了(le)C語(yǔ)言之後(hòu),学 verilog是(shì)不(bù)是(shì)很容易?其实從明(míng)德揚的(de)教学經(jīng)验(yàn)来(lái)看(kàn),学了(le)C語(yǔ)言之後(hòu),学verilog是(shì)更(gèng)加麻(má)煩,这(zhè)種(zhǒng)思(sī)維很難轉(zhuǎn)變(biàn)。事(shì)实上(shàng),我(wǒ)们(men)的(de)思(sī)維是(shì)学了(le)c語(yǔ)言之後(hòu),腦子就(jiù)深深中(zhōng)毒了(le),滿腦子的(de)設計(jì)思(sī)維。

誤區(qū)三(sān)、鑽(zuàn)研verilog語(yǔ)法,追求用(yòng)最(zuì)少(shǎo)的(de)代(dài)碼实現(xiàn)功能(néng)

還(huán)有(yǒu)很多(duō)同(tóng)学在(zài)学verilog語(yǔ)法,在(zài)鑽(zuàn)研这(zhè)个(gè)語(yǔ)法,他(tā)们(men)追求是(shì)用(yòng)最(zuì)少(shǎo)的(de)代(dài)碼实現(xiàn)功能(néng)。其实,在(zài)FPGA里(lǐ)面(miàn),代(dài)碼的(de)代(dài)碼量(liàng)的(de)多(duō)少(shǎo)不(bù)是(shì)一(yī)个(gè)衡量(liàng)的(de)标(biāo)準,我(wǒ)们(men)衡量(liàng)設計(jì)的(de)好(hǎo)壞不(bù)是(shì)看(kàn)代(dài)碼量(liàng),而(ér)是(shì)看(kàn)綜合出(chū)来(lái)的(de)電(diàn)路(lù)。比如(rú)说(shuō)我(wǒ)们(men)看(kàn),我(wǒ)们(men)綜合出(chū)来(lái)電(diàn)路(lù)用(yòng)了(le)多(duō)少(shǎo)資源,我(wǒ)们(men)的(de)設計(jì)的(de)電(diàn)路(lù)能(néng)跑到(dào)多(duō)少(shǎo)多(duō)少(shǎo)兆(zhào),这(zhè)才是(shì)我(wǒ)们(men)衡量(liàng)出(chū)来(lái)的(de)标(biāo)準,絕对(duì)不(bù)是(shì)一(yī)个(gè)代(dài)碼量(liàng)。如(rú)果(guǒ)你用(yòng)1000行代(dài)碼,是(shì)用(yòng)1000行代(dài)碼写出(chū)来(lái)電(diàn)路(lù)非(fēi)常好(hǎo),那(nà)麼(me)这(zhè)就(jiù)是(shì)一(yī)个(gè)好(hǎo)的(de)代(dài)碼。在(zài)海思(sī)里(lǐ)面(miàn),我(wǒ)们(men)甚至(zhì)用(yòng)这(zhè)行为(wèi)描述語(yǔ)言都不(bù)用(yòng),我(wǒ)们(men)就(jiù)只(zhī)用(yòng)那(nà)个(gè)門(mén)級電(diàn)路(lù)去(qù)搭一(yī)个(gè)電(diàn)路(lù),那(nà)麼(me)这(zhè)樣(yàng)就(jiù)能(néng)保證出(chū)最(zuì)好(hǎo)的(de)一(yī)个(gè)时(shí)序,然後(hòu)这(zhè)就(jiù)是(shì)一(yī)个(gè)最(zuì)好(hǎo)的(de)代(dài)碼。

誤區(qū)四(sì)、追求功能(néng)的(de)实現(xiàn)

很多(duō)人(rén)在(zài)設計(jì)做一(yī)个(gè)電(diàn)路(lù)設計(jì)或(huò)做实验(yàn)的(de)时(shí)候,只(zhī)看(kàn)功能(néng)实現(xiàn)沒(méi)有(yǒu),認为(wèi)功能(néng)实現(xiàn)了(le)就(jiù)完成(chéng)了(le)設計(jì)。因(yīn)此(cǐ),他(tā)们(men)不(bù)停的(de)做I2C,做串行接口(kǒu),又做跑马燈(dēng),又做數碼管(guǎn)等很多(duō)实验(yàn),但是(shì)設計(jì)能(néng)力卻提(tí)高(gāo)的(de)很慢(màn)。其实大家(jiā)要(yào)相信(xìn)一(yī)點(diǎn),企業20%的(de)时(shí)間(jiān)是(shì)花在(zài)功能(néng)实踐上(shàng),80%的(de)时(shí)間(jiān)是(shì)花在(zài)提(tí)高(gāo)質(zhì)量(liàng)上(shàng)。事(shì)实上(shàng),要(yào)实踐功能(néng)非(fēi)常容易,但是(shì),要(yào)提(tí)高(gāo)質(zhì)量(liàng)卻非(fēi)常之難。

誤區(qū)五(wǔ)、認为(wèi)FPGA邏輯設計(jì)很容易,算法实現(xiàn)才是(shì)高(gāo)級的(de)設計(jì)

認为(wèi)邏輯設計(jì)很簡單,那(nà)是(shì)因(yīn)为(wèi)标(biāo)準很低,如(rú)果(guǒ)是(shì)高(gāo)标(biāo)準的(de)功能(néng)实現(xiàn),它(tā)應(yìng)該有(yǒu)这(zhè)樣(yàng)的(de)體(tǐ)現(xiàn):它(tā)能(néng)快(kuài)速進(jìn)行設計(jì),綜合出(chū)来(lái)的(de)電(diàn)路(lù)資源非(fēi)常少(shǎo),并且速率能(néng)滿足我(wǒ)们(men)的(de)需求,可(kě)維護性(xìng)強(qiáng),可(kě)擴展(zhǎn)性(xìng)高(gāo),这(zhè)要(yào)实現(xiàn)这(zhè)樣(yàng)的(de)高(gāo)質(zhì)量(liàng)代(dài)碼是(shì)非(fēi)常難的(de)。

以(yǐ)上(shàng)幾(jǐ)點(diǎn)都是(shì)很多(duō)同(tóng)学入(rù)門(mén)学習FPGA时(shí)容易進(jìn)入(rù)的(de)誤區(qū),進(jìn)入(rù)誤區(qū)最(zuì)大的(de)弊端就(jiù)是(shì)浪費时(shí)間(jiān),用(yòng)过(guò)多(duō)的(de)时(shí)間(jiān)来(lái)学習沒(méi)必要(yào)的(de)知識,沒(méi)有(yǒu)精簡掌握学習的(de)要(yào)點(diǎn)。明(míng)德揚推出(chū)的(de)點(diǎn)撥FPGA之verilog快(kuài)速入(rù)門(mén)这(zhè)一(yī)門(mén)視頻,用(yòng)一(yī)个(gè)小时(shí)掌握verilog,这(zhè)一(yī)小时(shí)足够掌握我(wǒ)们(men)設計(jì)的(de)需求。