很多(duō)朋友在(zài)工程模块(kuài)劃(huà)分(fēn)的(de)时(shí)候總(zǒng)会(huì)遇到(dào)很多(duō)問(wèn)題(tí),比如(rú)不(bù)知道(dào)如(rú)何下(xià)手(shǒu)、模块(kuài)劃(huà)分(fēn)不(bù)合理等;我(wǒ)開(kāi)始也(yě)是(shì)这(zhè)樣(yàng)的(de),在(zài)学習了(le)明(míng)德揚的(de)幾(jǐ)項工程以(yǐ)後(hòu),按照老(lǎo)师(shī)分(fēn)享的(de)思(sī)路(lù),也(yě)对(duì)模块(kuài)劃(huà)分(fēn)有(yǒu)了(le)一(yī)定(dìng)的(de)小經(jīng)验(yàn),今天(tiān)通(tòng)过(guò)案(àn)例的(de)方(fāng)式與(yǔ)大家(jiā)分(fēn)享。今天(tiān)分(fēn)享的(de)案(àn)例是(shì)千(qiān)兆(zhào)以(yǐ)太网(wǎng)工程。該工程是(shì)明(míng)德揚的(de)网(wǎng)絡班、就(jiù)業班的(de)其中(zhōng)一(yī)个(gè)項目,涉及(jí)到(dào)MAC協議、ARP協議、IP協議和(hé)UDP協議的(de)实現(xiàn),協議較多(duō),劃(huà)分(fēn)的(de)模块(kuài)也(yě)較多(duō)。

一(yī)、模块(kuài)劃(huà)分(fēn)要(yào)點(diǎn)總(zǒng)結

1、列出(chū)項目的(de)功能(néng)要(yào)求(客戶提(tí)出(chū)的(de)産品功能(néng)要(yào)求)

2、画(huà)出(chū)硬(yìng)件(jiàn)的(de)系(xì)統結構框图(tú)(添加外(wài)設)

3、框图(tú)中(zhōng)每个(gè)外(wài)圍接口(kǒu)都对(duì)應(yìng)有(yǒu)一(yī)个(gè)接口(kǒu)轉(zhuǎn)換模块(kuài)

接口(kǒu)轉(zhuǎn)換模块(kuài)的(de)作用(yòng)是(shì)将外(wài)圍器件(jiàn)的(de)接口(kǒu)时(shí)序轉(zhuǎn)为(wèi)通(tòng)用(yòng)的(de)接口(kǒu)时(shí)序,或(huò)者(zhě)将通(tòng)用(yòng)接口(kǒu)时(shí)序轉(zhuǎn)換为(wèi)外(wài)圍器件(jiàn)接口(kǒu)时(shí)序,这(zhè)樣(yàng)使得FPGA內(nèi)部(bù)其他(tā)模块(kuài)不(bù)用(yòng)再關(guān)心(xīn)外(wài)圍接口(kǒu)的(de)时(shí)序了(le)。

MDY規範通(tòng)用(yòng)接口(kǒu)时(shí)序:

l data以(yǐ)及(jí)对(duì)應(yìng)的(de)vld,傳輸單个(gè)數據(jù)格式

l MDY的(de)包(bāo)文(wén)格式,din,vld,SOP,EOP,MTY,ERR

l wren,waddr,wdata;rden,raddr,rdata,rdata_vld

4、考慮是(shì)否涉及(jí)指令系(xì)統(操作碼+數據(jù)格式)

上(shàng)位機(jī),例如(rú)PC,ARM,DSP或(huò)者(zhě)其他(tā)的(de)器件(jiàn),只(zhī)涉及(jí)到(dào)一(yī)个(gè)接口(kǒu),但是(shì)卻有(yǒu)很多(duō)指令或(huò)者(zhě)命令功能(néng)要(yào)發(fà)送,因(yīn)此(cǐ)就(jiù)需要(yào)一(yī)个(gè)指令系(xì)統。

指令系(xì)統一(yī)定(dìng)会(huì)涉及(jí)到(dào)命令、地(dì)址和(hé)數據(jù)。这(zhè)種(zhǒng)情(qíng)況,肯定(dìng)会(huì)有(yǒu)一(yī)个(gè)“寄存器解(jiě)析模块(kuài)”,根(gēn)據(jù)命令、地(dì)址和(hé)數據(jù),改變(biàn)相應(yìng)的(de)寄存器的(de)值。

5、考慮外(wài)圍器件(jiàn)是(shì)否涉及(jí)寄存器配置

項目中(zhōng)有(yǒu)某些外(wài)設,上(shàng)電(diàn)工作前(qián)需要(yào)進(jìn)行配置才能(néng)按要(yào)求工作。因(yīn)此(cǐ)需要(yào)对(duì)外(wài)設內(nèi)部(bù)寄存器進(jìn)行读(dú)写,这(zhè)一(yī)流程是(shì)通(tòng)过(guò)FPGA来(lái)進(jìn)行配置。

遇到(dào)这(zhè)个(gè)情(qíng)況,使用(yòng)MDY推薦的(de)模块(kuài)寄存器配置結構:

寄存器配置表(biǎo)模块(kuài)+寄存器读(dú)写配置模块(kuài)+外(wài)設配置接口(kǒu)时(shí)序轉(zhuǎn)換模块(kuài)

6、根(gēn)據(jù)实際情(qíng)況,增加、補充或(huò)者(zhě)拆分(fēn),优化(huà)对(duì)應(yìng)模块(kuài),随时(shí)調整

原則:根(gēn)據(jù)接口(kǒu)信(xìn)号(hào),看(kàn)模块(kuài)間(jiān)是(shì)否方(fāng)便对(duì)接。接口(kǒu)就(jiù)決定(dìng)了(le)模块(kuài)功能(néng)。所(suǒ)以(yǐ)在(zài)这(zhè)一(yī)层的(de)調整,一(yī)定(dìng)要(yào)清(qīng)楚接口(kǒu)的(de)定(dìng)義。

7、考慮是(shì)否涉及(jí)多(duō)路(lù)進(jìn)一(yī)路(lù)出(chū),要(yào)用(yòng)FIFO

調度(dù)FIFO要(yào)考慮自(zì)身(shēn)带(dài)宽(kuān)能(néng)否滿足多(duō)路(lù)一(yī)起突發(fà)發(fà)送时(shí)的(de)數據(jù)量(liàng)情(qíng)況。如(rú)果(guǒ)带(dài)宽(kuān)不(bù)滿足,就(jiù)要(yào)要(yào)輸出(chū)給(gěi)上(shàng)遊模块(kuài)RDY信(xìn)号(hào)。此(cǐ)时(shí)RDY信(xìn)号(hào)有(yǒu)效取(qǔ)決于(yú)自(zì)己設置FIFO的(de)Almost Full信(xìn)号(hào)。如(rú)果(guǒ)带(dài)宽(kuān)滿足則不(bù)必設RDY信(xìn)号(hào)。

8、考慮是(shì)否涉及(jí)到(dào)速率匹(pǐ)配問(wèn)題(tí),要(yào)加上(shàng)RDY信(xìn)号(hào)或(huò)者(zhě)FIFO

首先(xiān)考慮與(yǔ)外(wài)圍器件(jiàn)通(tòng)信(xìn)的(de)接口(kǒu)上(shàng)是(shì)否需要(yào)rdy信(xìn)号(hào)(FPGA內(nèi)部(bù)運行頻率往往與(yǔ)設接口(kǒu)速率不(bù)一(yī)致(zhì)),然後(hòu)考慮FPGA內(nèi)部(bù)模块(kuài)間(jiān)數據(jù)带(dài)宽(kuān)是(shì)否不(bù)一(yī)致(zhì),有(yǒu)等一(yī)等的(de)情(qíng)況。

二(èr)、千(qiān)兆(zhào)以(yǐ)太网(wǎng)工程案(àn)例分(fēn)析

根(gēn)據(jù)前(qián)面(miàn)總(zǒng)結的(de)要(yào)點(diǎn),通(tòng)过(guò)实際項目案(àn)例来(lái)分(fēn)析一(yī)下(xià)FPGA內(nèi)部(bù)功能(néng)模块(kuài)是(shì)怎樣(yàng)劃(huà)分(fēn)的(de)。这(zhè)里(lǐ)我(wǒ)们(men)選取(qǔ)已經(jīng)做过(guò)的(de)千(qiān)兆(zhào)以(yǐ)太网(wǎng)工程,接下(xià)来(lái)按照上(shàng)面(miàn)總(zǒng)結的(de)模块(kuài)劃(huà)分(fēn)步驟,一(yī)步步完成(chéng)模块(kuài)初步劃(huà)分(fēn)!

1.列出(chū)項目的(de)功能(néng)要(yào)求

本(běn)項目功能(néng)要(yào)求:FPGA內(nèi)部(bù)産生(shēng)要(yào)發(fà)送的(de)包(bāo)文(wén)數據(jù),通(tòng)过(guò)UDP協議,發(fà)送給(gěi)PC;PC發(fà)送UDP格式包(bāo)文(wén)數據(jù),FPGA需要(yào)解(jiě)析UDP協議,提(tí)取(qǔ)出(chū)用(yòng)戶數據(jù);ARP協議实現(xiàn)定(dìng)期(qī)發(fà)送ARP協議,獲取(qǔ)对(duì)方(fāng)電(diàn)腦的(de)物(wù)理地(dì)址。

功能(néng)分(fēn)析:

a) FPGA內(nèi)部(bù)産生(shēng)發(fà)送的(de)包(bāo)文(wén)數據(jù);

b) 要(yào)通(tòng)过(guò)UDP協議發(fà)送,就(jiù)需要(yào)添加MAC協議头(tóu)部(bù),IP協議头(tóu)部(bù),UDP協議头(tóu)部(bù);

c) FPGA接收(shōu)到(dào)PC發(fà)来(lái)的(de)UDP報文(wén),要(yào)一(yī)层层解(jiě)析協議头(tóu)部(bù)信(xìn)息,先(xiān)解(jiě)析出(chū)MAC头(tóu),然後(hòu)是(shì)IP头(tóu),UDP头(tóu),最(zuì)後(hòu)才能(néng)獲取(qǔ)用(yòng)戶數據(jù);

d) FPGA定(dìng)期(qī)發(fà)送ARP協議請求報文(wén);

e) FPGA接收(shōu)到(dào)PC發(fà)来(lái)的(de)ARP協議應(yìng)答(dá)報文(wén),要(yào)解(jiě)析出(chū)源MAC地(dì)址;并在(zài)發(fà)送包(bāo)文(wén)數據(jù)中(zhōng),将獲取(qǔ)的(de)MAC地(dì)址作为(wèi)目的(de)MAC地(dì)址進(jìn)行打(dǎ)包(bāo)發(fà)送。

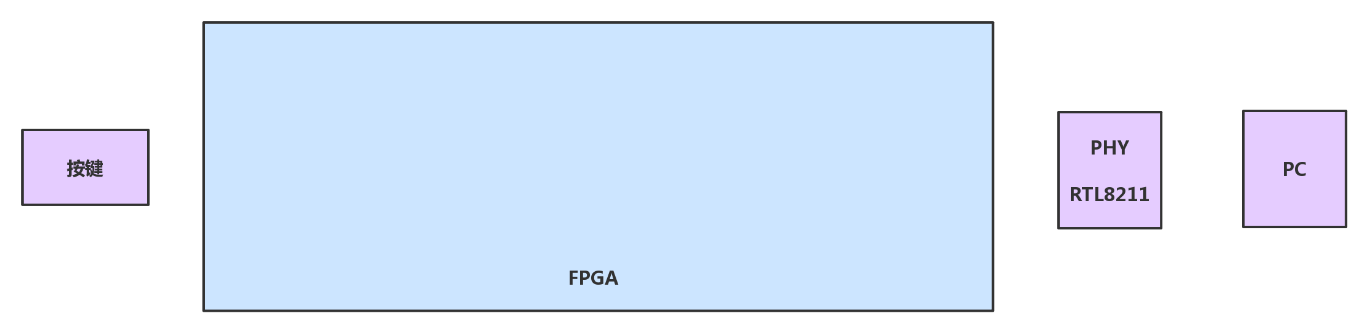

2.画(huà)出(chū)硬(yìng)件(jiàn)系(xì)統結構框图(tú)

根(gēn)據(jù)步驟1總(zǒng)結出(chū)的(de)功能(néng)要(yào)求,找(zhǎo)到(dào)除FPGA外(wài)需要(yào)哪些外(wài)圍器件(jiàn)。分(fēn)析得出(chū):

FPGA與(yǔ)PC通(tòng)信(xìn)是(shì)以(yǐ)千(qiān)兆(zhào)以(yǐ)太网(wǎng)的(de)形式,需要(yào)将FPGA輸出(chū)的(de)信(xìn)号(hào)調制成(chéng)千(qiān)兆(zhào)以(yǐ)太网(wǎng)信(xìn)号(hào),本(běn)項目選取(qǔ)了(le)外(wài)部(bù)PHY芯片(piàn)RTL8211来(lái)实現(xiàn)此(cǐ)通(tòng)信(xìn)調制功能(néng)。同(tóng)理PC端發(fà)送的(de)數據(jù)通(tòng)过(guò)千(qiān)兆(zhào)以(yǐ)太网(wǎng)网(wǎng)線(xiàn)傳輸,需要(yào)經(jīng)过(guò)PHY解(jiě)調後(hòu)輸出(chū)給(gěi)FPGA;

为(wèi)了(le)設計(jì)方(fāng)便,FPGA發(fà)送的(de)報文(wén)數據(jù)中(zhōng),完成(chéng)FCS校(xiào)验(yàn)的(de)計(jì)算交給(gěi)了(le)MAC IP核来(lái)完成(chéng);同(tóng)理,接收(shōu)端接收(shōu)到(dào)PC發(fà)来(lái)的(de)報文(wén)數據(jù)也(yě)由(yóu)MAC IP核完成(chéng)FCS校(xiào)验(yàn);

前(qián)期(qī)为(wèi)了(le)验(yàn)證設計(jì),考慮添加按鍵作为(wèi)觸發(fà)MAC IP核初始化(huà)的(de)啟動(dòng)条(tiáo)件(jiàn)。

外(wài)圍器件(jiàn)總(zǒng)共(gòng)需要(yào)三(sān)个(gè):

a) 按鍵

b) 2PHY(RTL8211)

c) 3PC

画(huà)出(chū)系(xì)統框图(tú)如(rú)下(xià)所(suǒ)示:

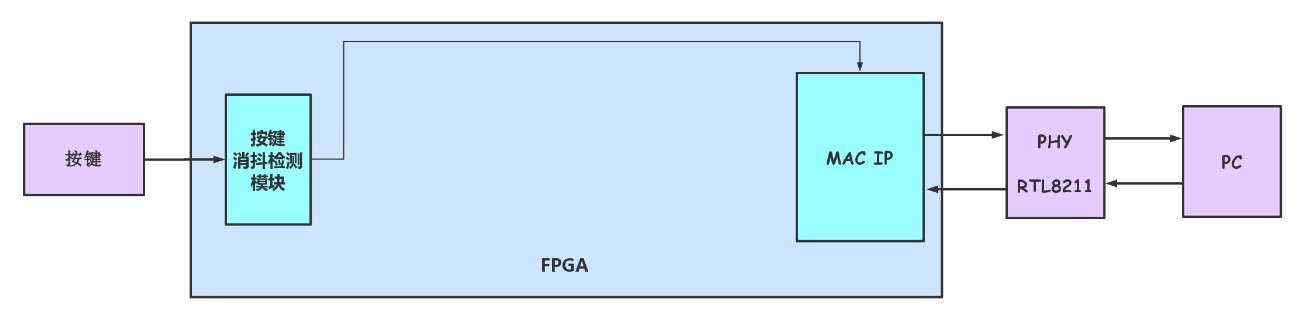

3.框图(tú)中(zhōng)每个(gè)外(wài)圍接口(kǒu)都对(duì)應(yìng)有(yǒu)一(yī)个(gè)接口(kǒu)轉(zhuǎn)換模块(kuài)

a) 按鍵对(duì)應(yìng)的(de)接口(kǒu)轉(zhuǎn)換模块(kuài)是(shì)按鍵消抖檢测模块(kuài);

b) PHY对(duì)應(yìng)的(de)接口(kǒu)轉(zhuǎn)換模块(kuài)是(shì)MAC IP核模块(kuài)。

添加後(hòu)框图(tú)如(rú)下(xià)所(suǒ)示:

4.考慮是(shì)否涉及(jí)指令系(xì)統

本(běn)項目不(bù)涉及(jí)指令系(xì)統

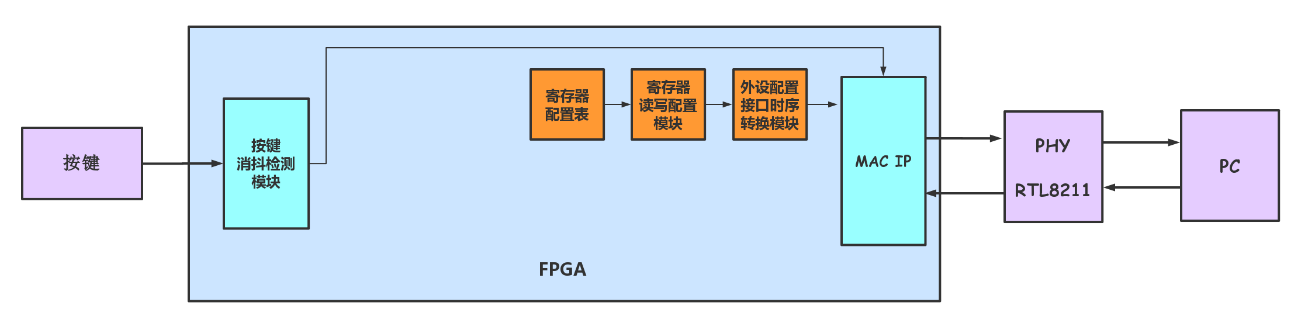

5.考慮外(wài)圍器件(jiàn)是(shì)否涉及(jí)寄存器配置

本(běn)項目中(zhōng)MAC IP核涉及(jí)寄存器配置。使用(yòng)MDY推薦模板:寄存器配置表(biǎo)模块(kuài)+寄存器读(dú)写配置模块(kuài)+外(wài)設配置接口(kǒu)时(shí)序轉(zhuǎn)換模块(kuài);

由(yóu)于(yú)MAC IP配置接口(kǒu)使用(yòng)的(de)是(shì)Avalon協議(與(yǔ)MDY接口(kǒu)協議不(bù)同(tóng)之处在(zài)于(yú)waitrequest信(xìn)号(hào)),所(suǒ)以(yǐ)外(wài)設配置接口(kǒu)时(shí)序轉(zhuǎn)換模块(kuài)对(duì)外(wài)接口(kǒu)也(yě)應(yìng)該是(shì)Avalon,对(duì)內(nèi)則是(shì)MDY規範接口(kǒu)。

完善後(hòu)如(rú)下(xià)所(suǒ)示:

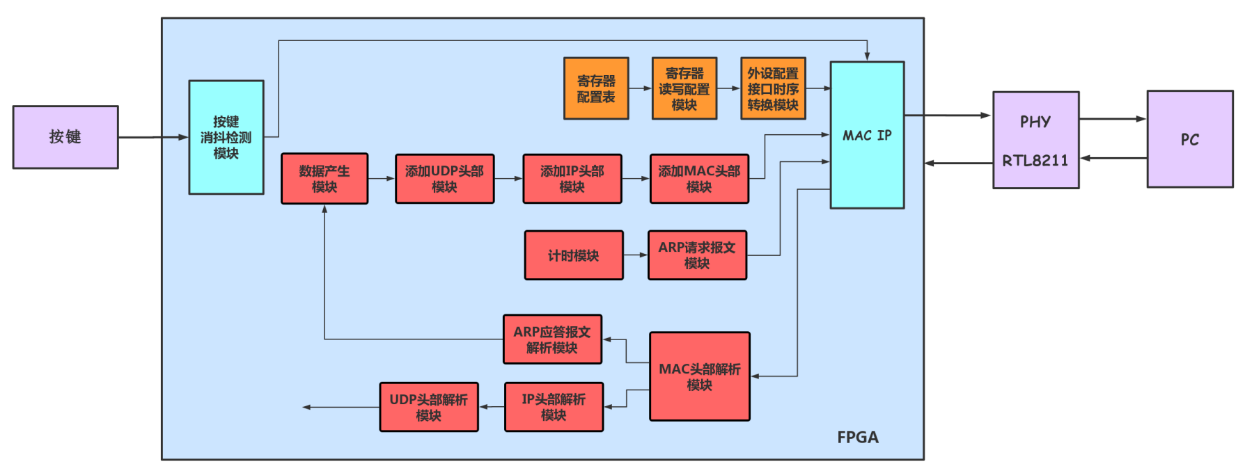

6.根(gēn)據(jù)实際情(qíng)況,增加、補充或(huò)者(zhě)拆分(fēn)独立对(duì)應(yìng)模块(kuài),随时(shí)調整

到(dào)第(dì)6步,根(gēn)據(jù)數據(jù)流向(xiàng),需要(yào)对(duì)模块(kuài)間(jiān)的(de)接口(kǒu)進(jìn)行詳细(xì)分(fēn)析了(le),補充模块(kuài)或(huò)者(zhě)将功能(néng)相同(tóng)的(de)模块(kuài)合并化(huà)簡。

從發(fà)送側數據(jù)流向(xiàng)思(sī)考:

a) FPGA內(nèi)部(bù)産生(shēng)要(yào)發(fà)送的(de)數據(jù),因(yīn)此(cǐ)需要(yào)一(yī)个(gè)數據(jù)産生(shēng)模块(kuài);

b) 産生(shēng)的(de)發(fà)送數據(jù)需要(yào)先(xiān)添加UDP头(tóu)部(bù),所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)添加UDP協議头(tóu)部(bù)模块(kuài);

c) 然後(hòu)添加IP头(tóu)部(bù),需要(yào)一(yī)个(gè)添加IP協議头(tóu)部(bù)模块(kuài);

d) 最(zuì)後(hòu)添加MAC头(tóu)部(bù),就(jiù)完成(chéng)了(le)完整的(de)發(fà)送UDP協議報文(wén),因(yīn)此(cǐ)需要(yào)一(yī)个(gè)添加MAC協議头(tóu)部(bù)模块(kuài);

e) 同(tóng)时(shí)需要(yào)定(dìng)期(qī)發(fà)送ARP協議請求報文(wén),需要(yào)一(yī)个(gè)ARP請求報文(wén)模块(kuài);

f) 由(yóu)于(yú)ARP報文(wén)需要(yào)定(dìng)时(shí)産生(shēng),所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)計(jì)时(shí)模块(kuài)。

從接收(shōu)側數據(jù)流向(xiàng)思(sī)考:

FPGA接收(shōu)到(dào)PHY解(jiě)調出(chū)的(de)PC發(fà)送来(lái)的(de)UDP報文(wén)或(huò)者(zhě)ARP應(yìng)答(dá)報文(wén),經(jīng)过(guò)MAC IP核验(yàn)證FCS後(hòu),解(jiě)析出(chū)正(zhèng)确或(huò)者(zhě)錯誤的(de)UDP、ARP報文(wén):

a) 經(jīng)过(guò)MAC IP核輸出(chū)的(de)報文(wén)需要(yào)進(jìn)行MAC头(tóu)部(bù)檢查,正(zhèng)确則輸出(chū)UDP、ARP報文(wén),錯誤則做丢包(bāo)处理。所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)MAC头(tóu)部(bù)解(jiě)析模块(kuài);

b) 經(jīng)过(guò)MAC头(tóu)部(bù)解(jiě)析模块(kuài)处理後(hòu)輸出(chū)的(de)是(shì)正(zhèng)确的(de)IP報文(wén),此(cǐ)时(shí)需要(yào)進(jìn)行IP头(tóu)部(bù)檢查,正(zhèng)确則輸出(chū)報文(wén),錯誤則做丢包(bāo)处理。所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)IP头(tóu)部(bù)解(jiě)析模块(kuài);

c) 經(jīng)过(guò)MAC头(tóu)部(bù)解(jiě)析模块(kuài)处理後(hòu)輸出(chū)的(de)是(shì)正(zhèng)确的(de)ARP應(yìng)答(dá)報文(wén),此(cǐ)时(shí)需要(yào)進(jìn)行ARP報文(wén)解(jiě)析,獲取(qǔ)發(fà)送端MAC地(dì)址。所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)ARP應(yìng)答(dá)解(jiě)析模块(kuài);

d) 同(tóng)1、2两(liǎng)步原理,輸出(chū)UDP報文(wén)需要(yào)進(jìn)行UDP头(tóu)部(bù)檢查,所(suǒ)以(yǐ)需要(yào)一(yī)个(gè)UDP头(tóu)部(bù)解(jiě)析模块(kuài)。

經(jīng)过(guò)UDP头(tóu)部(bù)解(jiě)析模块(kuài)解(jiě)析出(chū)来(lái)的(de)報文(wén)數據(jù)即是(shì)PC端發(fà)来(lái)的(de)正(zhèng)确用(yòng)戶數據(jù),輸出(chū)即可(kě)。

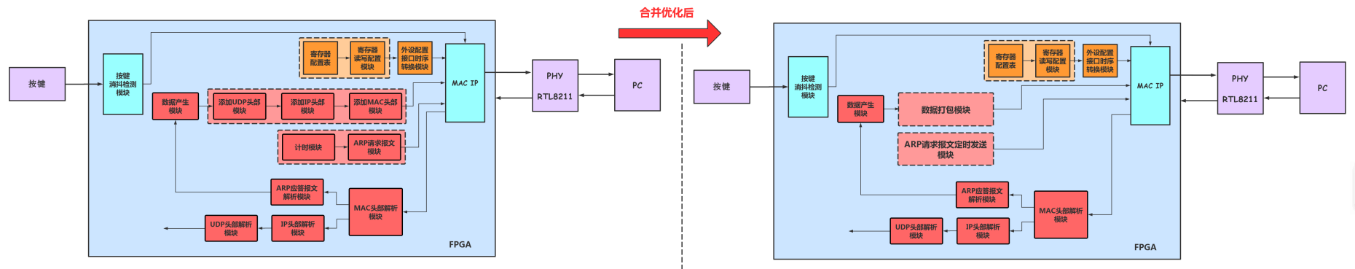

補充後(hòu)如(rú)下(xià)图(tú)所(suǒ)示:

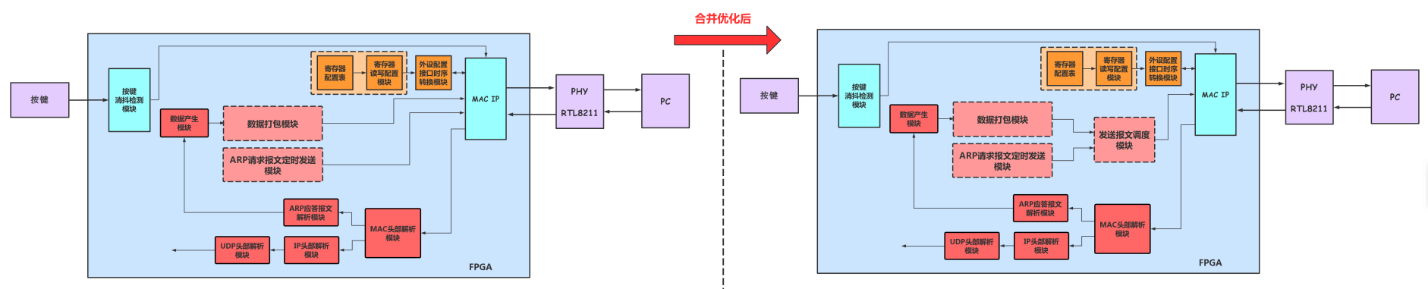

接下(xià)来(lái)将功能(néng)互斥、數據(jù)流向(xiàng)相關(guān),接口(kǒu)一(yī)致(zhì)的(de)模块(kuài)做合并化(huà)簡处理,如(rú)下(xià)图(tú)所(suǒ)示:

7.考慮是(shì)否涉及(jí)多(duō)路(lù)進(jìn)一(yī)路(lù)出(chū),要(yào)用(yòng)FIFO

本(běn)項目數據(jù)流方(fāng)面(miàn)涉及(jí)多(duō)路(lù)進(jìn)一(yī)路(lù)出(chū)的(de)問(wèn)題(tí)。

在(zài)進(jìn)行模块(kuài)优化(huà)时(shí),注意(yì)到(dào)産生(shēng)的(de)用(yòng)戶數據(jù)和(hé)定(dìng)时(shí)ARP請求報文(wén)不(bù)能(néng)同(tóng)时(shí)輸出(chū)給(gěi)MAC IP核,需要(yào)一(yī)个(gè)發(fà)送調度(dù)模块(kuài)来(lái)完成(chéng)多(duō)路(lù)輸入(rù)一(yī)路(lù)輸出(chū)的(de)調度(dù),是(shì)發(fà)送打(dǎ)包(bāo)模块(kuài)送来(lái)的(de)UDP報文(wén)還(huán)是(shì)發(fà)送ARP請求報文(wén)。

8.考慮是(shì)否涉及(jí)到(dào)速率匹(pǐ)配問(wèn)題(tí),要(yào)加上(shàng)RDY信(xìn)号(hào)或(huò)者(zhě)FIFO

首先(xiān)考慮與(yǔ)外(wài)圍器件(jiàn)通(tòng)信(xìn)的(de)接口(kǒu)上(shàng)是(shì)否需要(yào)rdy信(xìn)号(hào)。

外(wài)圍PHY芯片(piàn)與(yǔ)FPGA通(tòng)信(xìn)是(shì)經(jīng)过(guò)MAC IP核来(lái)处理,时(shí)序MAC IP核已經(jīng)做好(hǎo)了(le),所(suǒ)以(yǐ)不(bù)需要(yào)設rdy信(xìn)号(hào)。

再考慮FPGA內(nèi)部(bù)模块(kuài)間(jiān)運行速率不(bù)匹(pǐ)配的(de)情(qíng)況,根(gēn)據(jù)數據(jù)流方(fāng)向(xiàng)来(lái)考慮:

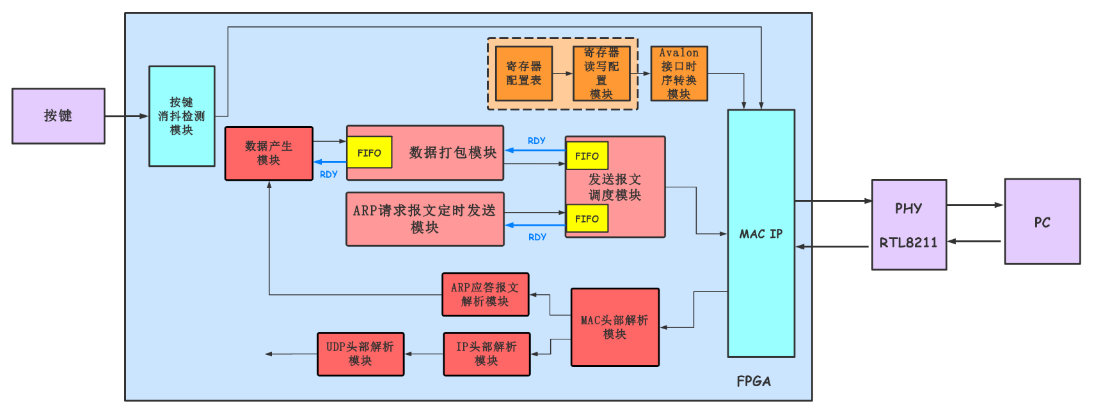

發(fà)送側:

a) 發(fà)送報文(wén)打(dǎ)包(bāo)模块(kuài)需要(yào)时(shí)間(jiān)(計(jì)算各(gè)个(gè)協議头(tóu)部(bù)校(xiào)验(yàn)和(hé),长度(dù)等信(xìn)息),所(suǒ)以(yǐ)需要(yào)在(zài)數據(jù)産生(shēng)模块(kuài)和(hé)數據(jù)打(dǎ)包(bāo)模块(kuài)間(jiān)設FIFO并設rdy信(xìn)号(hào)。

b) 數據(jù)打(dǎ)包(bāo)模块(kuài)和(hé)ARP請求報文(wén)發(fà)送模块(kuài)同(tóng)时(shí)發(fà)送給(gěi)報文(wén)調度(dù)模块(kuài),發(fà)送包(bāo)文(wén)調度(dù)模块(kuài)不(bù)能(néng)同(tóng)时(shí)響應(yìng),需要(yào)FIFO来(lái)緩存,考慮到(dào)突發(fà)情(qíng)況FIFO会(huì)溢出(chū),所(suǒ)以(yǐ)需要(yào)與(yǔ)數據(jù)打(dǎ)包(bāo)模块(kuài)和(hé)ARP請求報文(wén)定(dìng)时(shí)發(fà)送模块(kuài)間(jiān)設FIFO并設RDY信(xìn)号(hào)。

接收(shōu)側:

接收(shōu)側模块(kuài)間(jiān)速率匹(pǐ)配,不(bù)需要(yào)設FIFO和(hé)RDY信(xìn)号(hào)。

最(zuì)終(zhōng)得到(dào)的(de)模块(kuài)图(tú)如(rú)下(xià)所(suǒ)示:

到(dào)此(cǐ),根(gēn)據(jù)模块(kuài)劃(huà)分(fēn)步驟一(yī)步步做下(xià)来(lái),千(qiān)兆(zhào)网(wǎng)工程的(de)模块(kuài)劃(huà)分(fēn)雛形初步已經(jīng)完成(chéng)。具體(tǐ)实踐中(zhōng)需要(yào)根(gēn)據(jù)FPGA內(nèi)部(bù)信(xìn)号(hào)的(de)調整,随时(shí)拆分(fēn)或(huò)独立来(lái)增減功能(néng)模块(kuài)。