PCIE XDMA IP核介紹

本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处! 作者(zhě):雲(yún)哥哥

1.PCIE的(de)發(fà)送和(hé)接收(shōu)數據(jù)

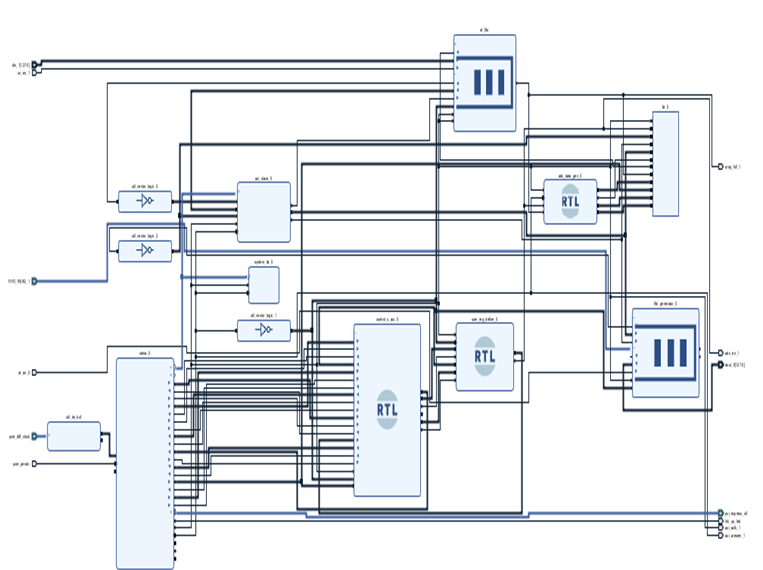

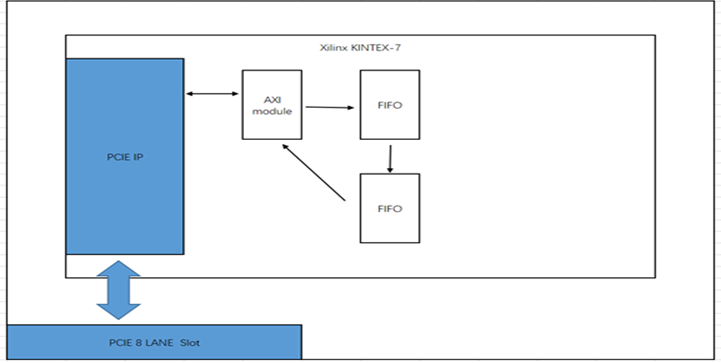

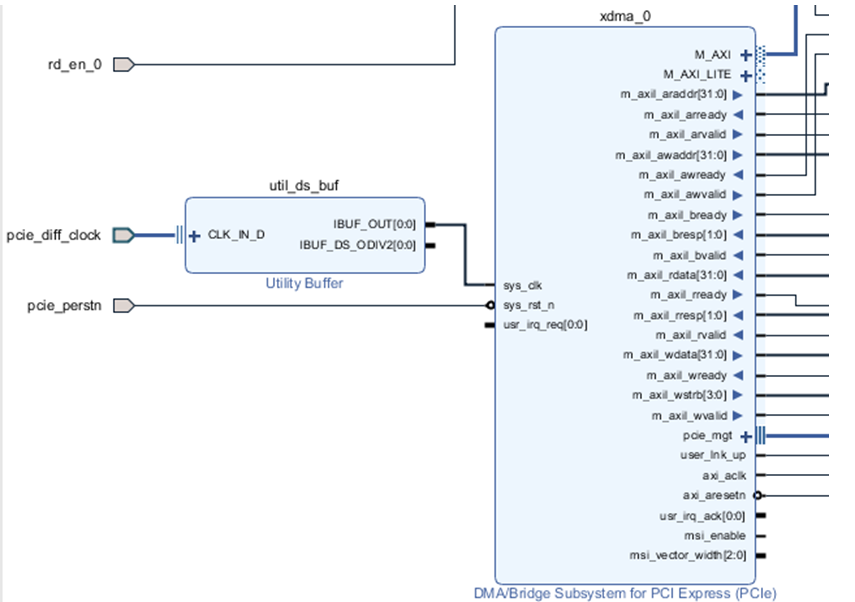

本(běn)工程的(de)目的(de)是(shì)在(zài)XC7K325tffg的(de)平台(tái)上(shàng)实現(xiàn)pcie的(de)數據(jù)發(fà)送和(hé)接收(shōu),速率8通(tòng)道(dào)2.5GB/s,首先(xiān)看(kàn)下(xià)本(běn)工程的(de)PCIE部(bù)分(fēn)的(de)結構:

架構

各(gè)个(gè)模块(kuài)的(de)作用(yòng)

PCIE部(bù)分(fēn)結構图(tú)

这(zhè)是(shì)PCIE IP核,主(zhǔ)要(yào)用(yòng)来(lái)發(fà)送數據(jù),發(fà)送引擎主(zhǔ)要(yào)負責将待發(fà)送數據(jù)按照PCIE協議組織成(chéng)不(bù)同(tóng)類(lèi)型的(de)TLP數據(jù)包(bāo),并發(fà)送給(gěi)PCIE IP核;發(fà)送DMA控制模块(kuài)主(zhǔ)要(yào)負責把DDR3中(zhōng)读(dú)取(qǔ)的(de)數據(jù)轉(zhuǎn)換成(chéng)TLP格式,并傳送給(gěi)發(fà)送引擎;接收(shōu)引擎用(yòng)于(yú)從PCIE IP核接收(shōu)不(bù)同(tóng)類(lèi)型的(de)TLP數據(jù),接收(shōu)DMA控制模块(kuài)用(yòng)于(yú)实現(xiàn)存儲器读(dú)請求包(bāo)的(de)發(fà)送流量(liàng)控制及(jí)接收(shōu)數據(jù)位宽(kuān)的(de)轉(zhuǎn)換;DMA狀态控制寄存器模块(kuài)主(zhǔ)要(yào)用(yòng)来(lái)解(jiě)析来(lái)自(zì)PC对(duì)模块(kuài)內(nèi)部(bù)寄存器的(de)命令和(hé)配置,并通(tòng)知發(fà)送引擎模块(kuài)、接收(shōu)引擎模块(kuài)及(jí)其他(tā)模块(kuài)作出(chū)相應(yìng)執行。

图(tú)表(biǎo) SEQ 图(tú)表(biǎo) \* ARABIC 1

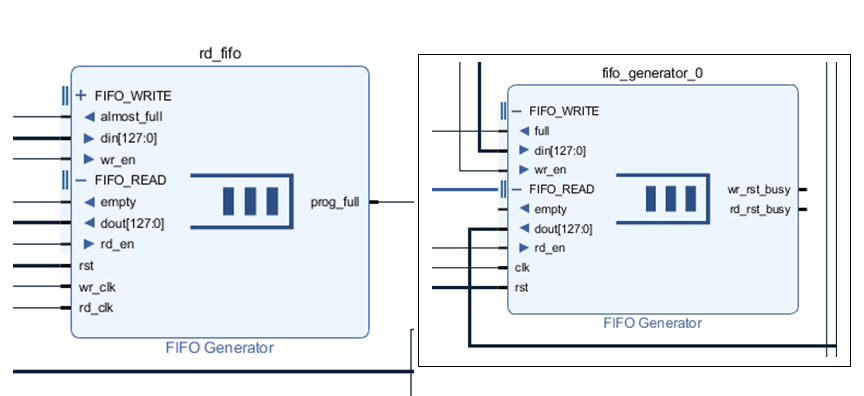

图(tú)表(biǎo)一(yī)中(zhōng) 左(zuǒ)图(tú)Rd_fifo是(shì)數據(jù)写入(rù)緩存模块(kuài),右(yòu)图(tú)是(shì)读(dú)出(chū)緩存數據(jù)模块(kuài)。

Fifo:先(xiān)入(rù)先(xiān)出(chū)隊列。數字(zì)電(diàn)路(lù)設計(jì)中(zhōng)所(suǒ)说(shuō)的(de)fifo实際是(shì)指fifo存儲器,主(zhǔ)要(yào)用(yòng)于(yú)數據(jù)緩存和(hé)异(yì)步处理,fifo存儲器緩存數據(jù)也(yě)遵循先(xiān)入(rù)先(xiān)出(chū)的(de)原則。Fifo本(běn)質(zhì)是(shì)一(yī)个(gè)RAM,它(tā)與(yǔ)普通(tòng)存儲器的(de)區(qū)别是(shì)沒(méi)有(yǒu)外(wài)部(bù)读(dú)写地(dì)址線(xiàn),这(zhè)樣(yàng)使用(yòng)起来(lái)非(fēi)常簡單,但缺點(diǎn)就(jiù)是(shì)只(zhī)能(néng)順序写入(rù)數據(jù),順序的(de)读(dú)写數據(jù)。

信(xìn)号(hào)列表(biǎo)

|

名稱 |

方(fāng)向(xiàng) |

位宽(kuān) |

说(shuō)明(míng) |

|

FIFO_read_1_empty |

o |

1 |

读(dú)fifo的(de)空信(xìn)号(hào)指示 1:读(dú)fifo里(lǐ)面(miàn)沒(méi)有(yǒu)數據(jù) 0:读(dú)fifo里(lǐ)面(miàn)有(yǒu)數據(jù) |

|

FIFO_READ_1_rd_data |

o |

128 |

读(dú)fifo數據(jù)的(de)輸出(chū) |

|

FIFO_READ_1_rd_en |

i |

1 |

读(dú)fifo的(de)使能(néng) 1:读(dú)出(chū)读(dú)fifo里(lǐ)面(miàn)的(de)數據(jù) 0:不(bù)读(dú)數據(jù) |

|

adc_en_1 |

o |

1 |

接收(shōu)到(dào)的(de)寄存器使能(néng) 1:寄存器0x0收(shōu)到(dào)數據(jù)为(wèi)0x01 0:寄存器0x0收(shōu)到(dào)數據(jù)为(wèi)0x00 |

|

Axi_aclk_1 |

o |

1 |

PCIE 对(duì)外(wài)提(tí)供的(de)用(yòng)戶时(shí)鐘(zhōng) |

|

axi_aresetn_1 |

o |

1 |

Pcie对(duì)外(wài)提(tí)供的(de)複位 |

|

din_1 |

i |

128 |

用(yòng)戶側想(xiǎng)要(yào)發(fà)送的(de)數據(jù)接口(kǒu) |

|

Lnk_up_led |

o |

1 |

Pcie連(lián)接指示信(xìn)号(hào) |

|

Pci_express_x8_rxn |

i |

8 |

Pcie的(de)接收(shōu)管(guǎn)脚n端 |

|

Pci_express_x8_rxp |

i |

8 |

Pcie的(de)接收(shōu)管(guǎn)脚p端 |

|

Pci_express_x8_txn |

o |

8 |

Pcie的(de)發(fà)送端n端 |

|

Pci_express_x8_txp |

o |

8 |

Pcie的(de)發(fà)送端p端 |

|

pcie_diff_dock_clk_n |

i |

1 |

Pcie时(shí)鐘(zhōng)信(xìn)号(hào)n端 |

|

Pcie_diff_dock_clk_p |

i |

1 |

Pcie时(shí)鐘(zhōng)信(xìn)号(hào)p端 |

|

Pcie_perstn |

i |

1 |

Pcie得複位管(guǎn)脚 |

|

Prog_full_1 |

o |

1 |

写fifo的(de)滿信(xìn)号(hào) |

|

wr_en_1 |

i |

1 |

写fifo的(de)写使能(néng) |

以(yǐ)上(shàng)就(jiù)是(shì)pcie xdma ip核介紹,想(xiǎng)要(yào)学習更(gèng)多(duō)內(nèi)容的(de)同(tóng)学,可(kě)以(yǐ)加Q:1465617980 雲(yún)哥哥 了(le)解(jiě)更(gèng)加專業的(de)知識!