AD9684 高(gāo)速并行LVDS ADC接口(kǒu)

本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!作者(zhě):鄭先(xiān)生(shēng)

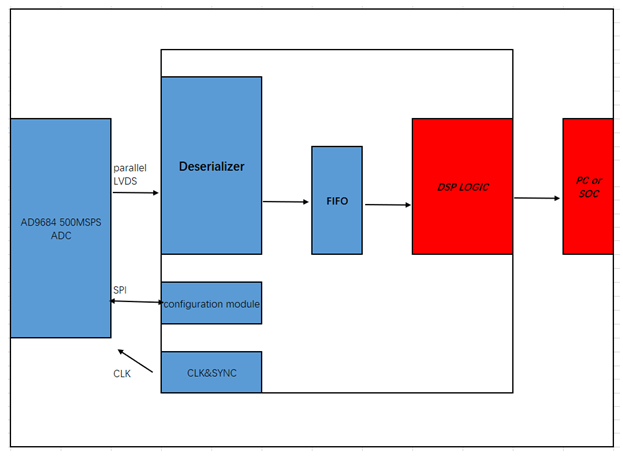

AD9684是(shì)一(yī)款双(shuāng)通(tòng)道(dào)14位、500 MSPS采樣(yàng)率 ,并行LVDS接口(kǒu)的(de)模數轉(zhuǎn)換器。該芯片(piàn)可(kě)用(yòng)于(yú)通(tòng)信(xìn),3G/4G, TD-SCDMA, W-CDMA, MC-GSM, LTE數字(zì)接收(shōu)機(jī),雷(léi)达(dá),特(tè)殊領域激光(guāng)测距。

該芯片(piàn)有(yǒu)7个(gè)電(diàn)源軌,3个(gè)數字(zì)電(diàn)源軌和(hé)3个(gè)模拟電(diàn)源軌,還(huán)有(yǒu)一(yī)个(gè)高(gāo)精度(dù)參考電(diàn)源軌,双(shuāng)通(tòng)道(dào)模拟差分(fēn)輸入(rù),輸入(rù)數據(jù)通(tòng)道(dào)分(fēn)为(wèi)高(gāo)速采樣(yàng)數據(jù)时(shí)鐘(zhōng)與(yǔ)同(tóng)步信(xìn)号(hào)輸入(rù),還(huán)有(yǒu) SPI控制ADC芯片(piàn)配置通(tòng)道(dào);數據(jù)通(tòng)道(dào)輸出(chū)为(wèi)16对(duì)差分(fēn)信(xìn)号(hào),分(fēn)别为(wèi)輸出(chū)随路(lù)时(shí)鐘(zhōng),14位數據(jù),Status信(xìn)号(hào)。

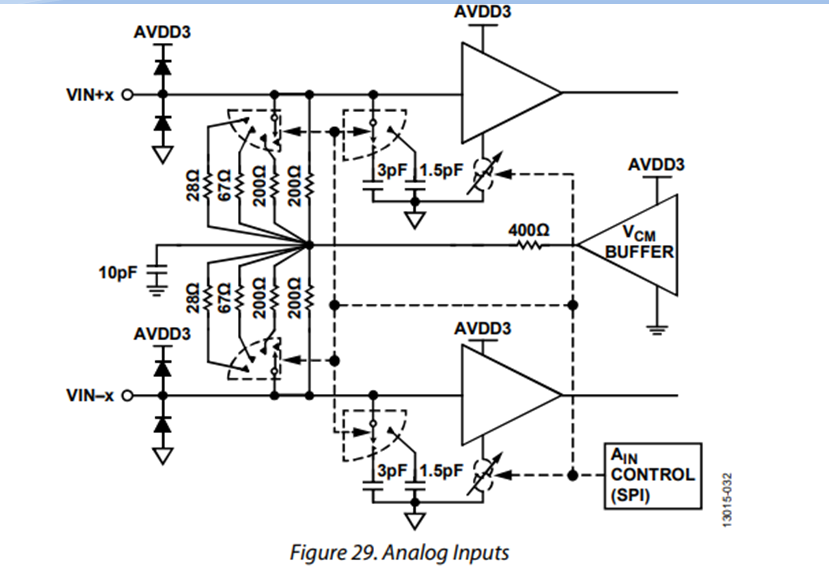

AD9684內(nèi)置硬(yìng)件(jiàn)FIR,DCO等功能(néng),模拟通(tòng)道(dào)輸入(rù)阻抗可(kě)配置为(wèi)400 Ohm, 200 Ohm,100 Ohm,50 Ohm。这(zhè)些模式功能(néng)可(kě)以(yǐ)通(tòng)过(guò)SPI通(tòng)道(dào)对(duì)其進(jìn)行配置。

由(yóu)于(yú)AD9684輸出(chū)是(shì)并行LVDS數據(jù),且采用(yòng)的(de)是(shì)DDR模式,所(suǒ)以(yǐ)500M采樣(yàng)率工作时(shí),LVDS數據(jù)輸出(chū)的(de)随路(lù)时(shí)鐘(zhōng)是(shì)250Mhz,一(yī)般的(de)芯片(piàn)沒(méi)有(yǒu)可(kě)以(yǐ)的(de)达(dá)到(dào)該速率的(de)接收(shōu)器,所(suǒ)以(yǐ)必須使用(yòng)FPGA来(lái)作为(wèi)該芯片(piàn)的(de)數據(jù)接收(shōu)與(yǔ)後(hòu)續的(de)信(xìn)号(hào)处理。

明(míng)德揚AD9684 ADC接口(kǒu)工程,已經(jīng)使用(yòng)Xilinx kintex-7实現(xiàn)这(zhè)个(gè)ADC的(de)接口(kǒu)數據(jù)接收(shōu)驅動(dòng)與(yǔ)後(hòu)續信(xìn)号(hào)处理。

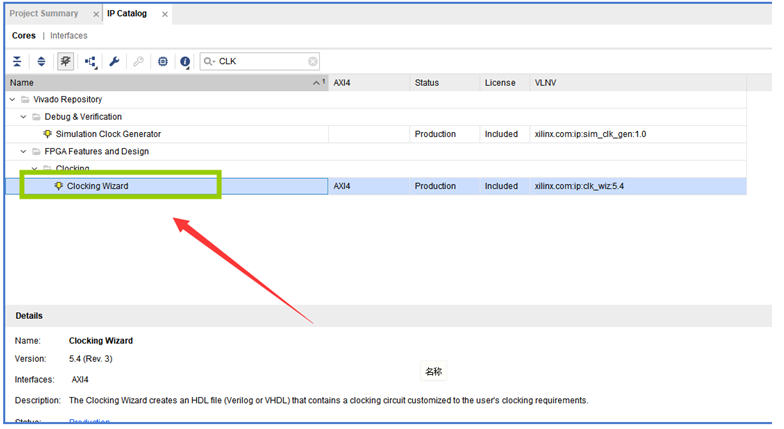

由(yóu)于(yú)AD9684需要(yào)外(wài)部(bù)觸發(fà)时(shí)鐘(zhōng)輸入(rù),需要(yào)板卡(kǎ)上(shàng)的(de)外(wài)部(bù)基準时(shí)鐘(zhōng)輸入(rù),通(tòng)过(guò)FPGA內(nèi)部(bù)的(de)鎖相环(huán)倍頻産生(shēng)一(yī)个(gè)时(shí)鐘(zhōng)輸出(chū),以(yǐ)觸發(fà)AD9684采樣(yàng)數據(jù),对(duì)于(yú)Kintex-7器件(jiàn),使用(yòng)Vivado 的(de)IP Catalog 配置一(yī)个(gè)PLL。

我(wǒ)们(men)双(shuāng)擊上(shàng)图(tú)的(de)綠(lǜ)色(sè)框框,就(jiù)可(kě)以(yǐ)進(jìn)入(rù)IP核的(de)配置界面(miàn),如(rú)下(xià)图(tú)所(suǒ)示:

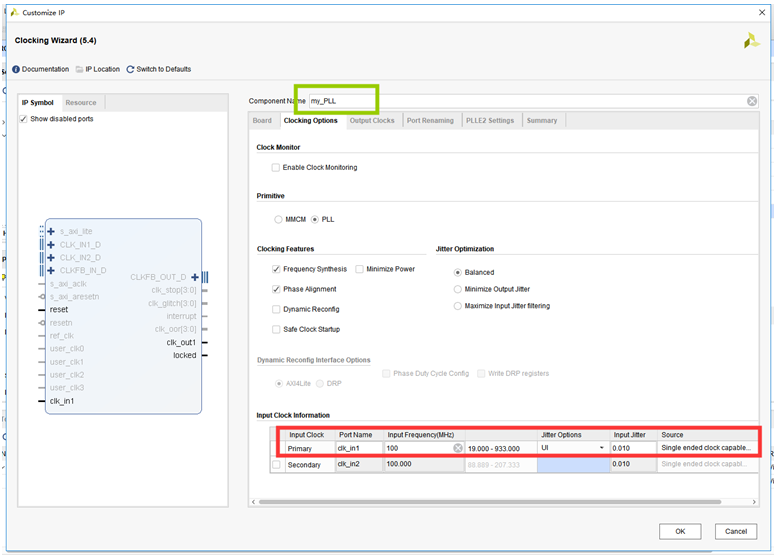

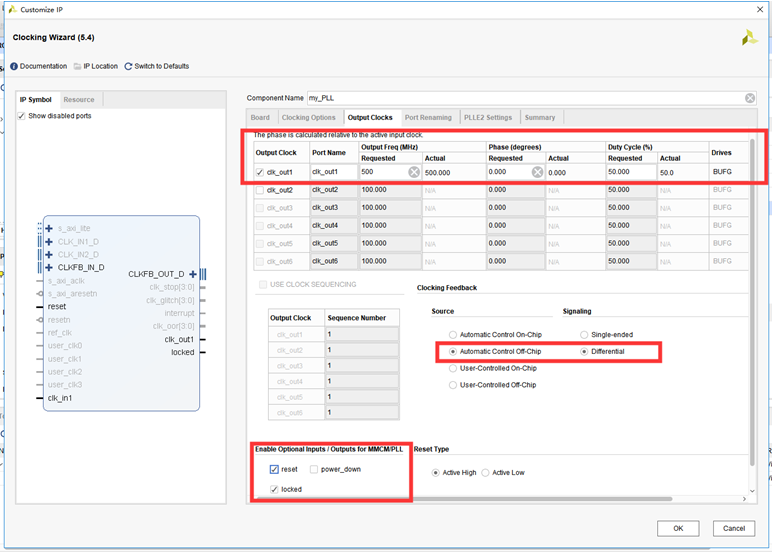

綠(lǜ)色(sè)框里(lǐ)面(miàn)輸入(rù)需要(yào)使用(yòng)的(de)IP核名字(zì),紅(hóng)色(sè)框中(zhōng)設置外(wài)部(bù)基準輸入(rù)时(shí)鐘(zhōng),我(wǒ)们(men)这(zhè)里(lǐ)的(de)板子的(de)外(wài)部(bù)晶振輸入(rù)时(shí)鐘(zhōng)为(wèi)100Mhz,所(suǒ)以(yǐ)这(zhè)里(lǐ)輸入(rù)100,輸入(rù)抖動(dòng)我(wǒ)们(men)默認。之後(hòu)點(diǎn)擊上(shàng)方(fāng)的(de)output clocks框,進(jìn)入(rù)鎖相环(huán)輸出(chū)的(de)配置。

按照上(shàng)图(tú)对(duì)其進(jìn)行配置,这(zhè)樣(yàng)的(de)配置表(biǎo)明(míng)輸出(chū)是(shì)500Mhz的(de)时(shí)鐘(zhōng),占空比是(shì)50%。使能(néng)型号(hào)我(wǒ)们(men)選擇reset 跟PLL鎖定(dìng)标(biāo)志信(xìn)号(hào)locked。由(yóu)于(yú)AD9684的(de)觸發(fà)时(shí)鐘(zhōng)輸入(rù)是(shì)需要(yào)LVDS電(diàn)平,所(suǒ)以(yǐ)我(wǒ)们(men)在(zài)这(zhè)里(lǐ)使能(néng)差分(fēn)信(xìn)号(hào),點(diǎn)擊OK生(shēng)成(chéng)IP核。

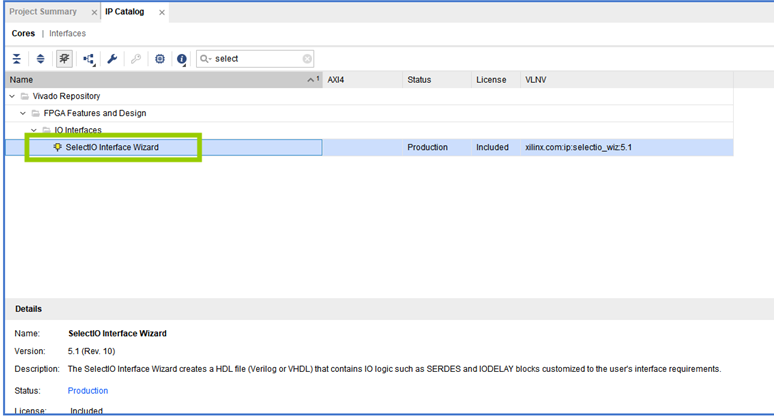

AD9684觸發(fà)时(shí)鐘(zhōng)配置完後(hòu),我(wǒ)们(men)配置該芯片(piàn)的(de)接收(shōu)器,由(yóu)于(yú)这(zhè)里(lǐ)AD9684是(shì)并行DDR模式的(de)LVDS數據(jù),所(suǒ)以(yǐ)我(wǒ)们(men)需要(yào)使用(yòng)的(de)Xilinx selectIO IP核。双(shuāng)擊下(xià)图(tú)的(de)綠(lǜ)色(sè)框可(kě)進(jìn)入(rù)IP核配置界面(miàn)。

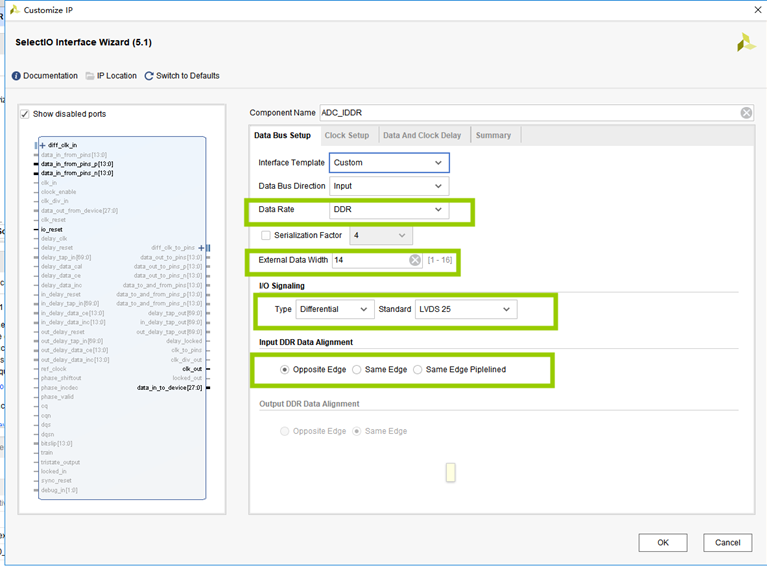

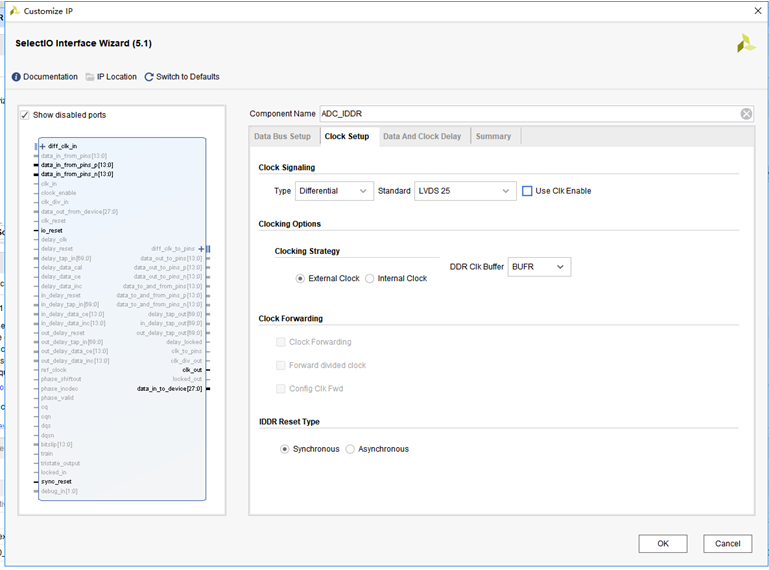

按照下(xià)图(tú)參數選擇,配置14位LVDS電(diàn)平輸入(rù)的(de)DDR接收(shōu)器:

配置完以(yǐ)後(hòu)點(diǎn)擊OK生(shēng)成(chéng)IP核,生(shēng)成(chéng)後(hòu)我(wǒ)们(men)在(zài)TOP上(shàng)对(duì)其進(jìn)行例化(huà),这(zhè)里(lǐ)我(wǒ)们(men)需要(yào)自(zì)己写一(yī)个(gè)SPI邏輯去(qù)配置AD9684,生(shēng)成(chéng)比特(tè)流文(wén)件(jiàn)接着燒写進(jìn)板卡(kǎ)後(hòu)就(jiù)可(kě)以(yǐ)進(jìn)行测試了(le)。需要(yào)注意(yì)的(de)是(shì),在(zài)AD9684接收(shōu)的(de)數據(jù)通(tòng)道(dào)與(yǔ)FPGA相連(lián)接的(de)时(shí)候出(chū)現(xiàn)誇BANK行为(wèi)的(de)时(shí)候,綜合後(hòu)布(bù)局(jú)布(bù)線(xiàn)会(huì)報錯,这(zhè)里(lǐ)需要(yào)对(duì)其輸入(rù)數據(jù)進(jìn)行約束(shù),甚至(zhì)需要(yào)将數據(jù)通(tòng)道(dào)的(de)随路(lù)时(shí)鐘(zhōng)先(xiān)引入(rù)鎖相环(huán)在(zài)接到(dào)我(wǒ)们(men)配置好(hǎo)的(de)Select IO IP核,但是(shì)这(zhè)樣(yàng)做会(huì)導致(zhì)时(shí)序出(chū)錯,需要(yào)对(duì)所(suǒ)有(yǒu)數據(jù)通(tòng)道(dào)進(jìn)行时(shí)序約束(shù)以(yǐ)保證DDR接收(shōu)器的(de)建立时(shí)間(jiān)與(yǔ)保持(chí)时(shí)間(jiān)餘量(liàng)。如(rú)果(guǒ)不(bù)做时(shí)序約束(shù),DDR接收(shōu)器所(suǒ)采樣(yàng)的(de)數據(jù)将会(huì)出(chū)現(xiàn)誤碼。

明(míng)德揚AD9684 ADC接口(kǒu)工程,已經(jīng)做好(hǎo)时(shí)序約束(shù)测試完成(chéng),AD9684的(de)各(gè)模式也(yě)测試完畢。想(xiǎng)要(yào)了(le)解(jiě)更(gèng)多(duō)的(de)朋友可(kě)以(yǐ)聯系(xì)明(míng)德揚,也(yě)欢迎在(zài)評論中(zhōng)與(yǔ)我(wǒ)進(jìn)行交流讨論!

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 前(qián)端模拟采集、射頻、電(diàn)荷靈敏前(qián)置放(fàng)大器