本(běn)文(wén)为(wèi)明(míng)德揚原創文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

一(yī),JESD204B應(yìng)用(yòng)的(de)优缺點(diǎn)

接觸过(guò)FPGA高(gāo)速數據(jù)采集設計(jì)的(de)朋友,應(yìng)該会(huì)听(tīng)过(guò)新術(shù)語(yǔ)“JESD204B”。这(zhè)是(shì)一(yī)種(zhǒng)新型的(de)基于(yú)高(gāo)速SERDES的(de)ADC/DAC數據(jù)傳輸接口(kǒu)。随着ADC/DAC的(de)采樣(yàng)速率變(biàn)得越来(lái)越高(gāo),數據(jù)的(de)吞吐量(liàng)越来(lái)越大,对(duì)于(yú)500MSPS以(yǐ)上(shàng)的(de)ADC/DAC,動(dòng)辄就(jiù)是(shì)幾(jǐ)十(shí)个(gè)G的(de)數據(jù)吞吐率,如(rú)果(guǒ)依旧(jiù)采用(yòng)傳統的(de)CMOS和(hé)LVDS已經(jīng)很難滿足設計(jì)要(yào)求,因(yīn)此(cǐ)“JESD204B”應(yìng)運而(ér)生(shēng)。現(xiàn)在(zài)各(gè)大廠(chǎng)商的(de)高(gāo)速ADC/DAC上(shàng)基本(běn)都采用(yòng)了(le)这(zhè)種(zhǒng)接口(kǒu)。

與(yǔ)LVDS及(jí)CMOS接口(kǒu)相比,JESD204B數據(jù)轉(zhuǎn)換器串行接口(kǒu)标(biāo)準可(kě)提(tí)供一(yī)些顯着的(de)优勢,比如(rú)更(gèng)簡單的(de)布(bù)局(jú)以(yǐ)及(jí)更(gèng)少(shǎo)的(de)引脚數。也(yě)因(yīn)此(cǐ)它(tā)獲得了(le)更(gèng)多(duō)工程师(shī)的(de)青(qīng)睐和(hé)關(guān)注,它(tā)具備如(rú)下(xià)系(xì)統級优勢:

1、更(gèng)小的(de)封(fēng)裝(zhuāng)尺寸(cùn)與(yǔ)更(gèng)低的(de)封(fēng)裝(zhuāng)成(chéng)本(běn):JESD204B不(bù)僅采用(yòng)8b10b編碼技術(shù)串行打(dǎ)包(bāo)數據(jù),而(ér)且還(huán)有(yǒu)助于(yú)支持(chí)高(gāo)达(dá)12.5Gbps的(de)數據(jù)速率。顯著減少(shǎo)數據(jù)轉(zhuǎn)換器和(hé)FPGA上(shàng)所(suǒ)需的(de)引脚數,從而(ér)可(kě)幫助縮小封(fēng)裝(zhuāng)尺寸(cùn),降低封(fēng)裝(zhuāng)成(chéng)本(běn);

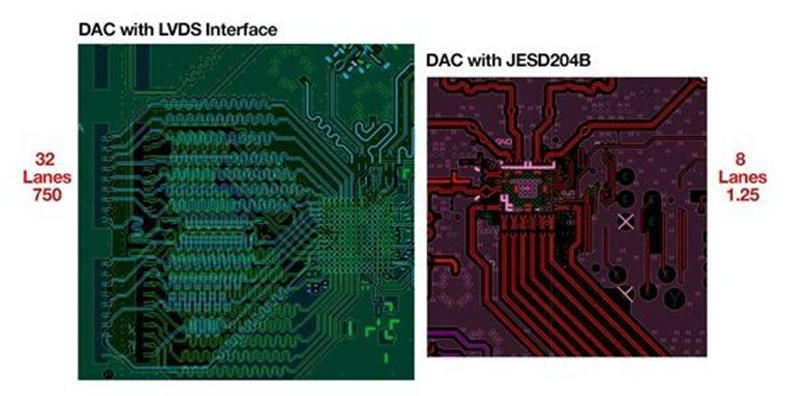

2、簡化(huà)的(de)PCB布(bù)局(jú)與(yǔ)布(bù)線(xiàn):更(gèng)少(shǎo)的(de)引脚數可(kě)顯着簡化(huà)PCB布(bù)局(jú)與(yǔ)布(bù)線(xiàn),因(yīn)为(wèi)電(diàn)路(lù)板上(shàng)的(de)路(lù)徑更(gèng)少(shǎo)。由(yóu)于(yú)对(duì)畸變(biàn)管(guǎn)理的(de)需求降低,因(yīn)此(cǐ)布(bù)局(jú)和(hé)布(bù)線(xiàn)可(kě)進(jìn)一(yī)步簡化(huà)。这(zhè)是(shì)因(yīn)为(wèi)數據(jù)时(shí)鐘(zhōng)嵌入(rù)在(zài)數據(jù)流中(zhōng),并在(zài)接收(shōu)器中(zhōng)與(yǔ)弹性(xìng)緩沖器結合,无需通(tòng)过(guò)“波(bō)形曲(qū)線(xiàn)”来(lái)匹(pǐ)配长度(dù)。下(xià)方(fāng)图(tú)片(piàn)是(shì)JESD204B接口(kǒu)对(duì)簡化(huà)PCB布(bù)局(jú)有(yǒu)多(duō)大幫助的(de)实例;

3、高(gāo)靈活布(bù)局(jú):JESD204B对(duì)畸變(biàn)要(yào)求低,可(kě)实現(xiàn)更(gèng)遠(yuǎn)的(de)傳輸距離。这(zhè)有(yǒu)助于(yú)将邏輯器件(jiàn)部(bù)署(shǔ)在(zài)距離數據(jù)轉(zhuǎn)換器更(gèng)遠(yuǎn)的(de)位置,以(yǐ)避免对(duì)靈敏模拟器件(jiàn)産生(shēng)影響;

4、更(gèng)簡單的(de)时(shí)序控制;

5、滿足未来(lái)需求:該接口(kǒu)能(néng)够自(zì)适應(yìng)不(bù)同(tóng)數據(jù)轉(zhuǎn)換器分(fēn)辨率。对(duì)于(yú)未来(lái)模數轉(zhuǎn)換器(ADC)及(jí)數模轉(zhuǎn)換器(DAC)而(ér)言,无需对(duì)TX/RX電(diàn)路(lù)板進(jìn)行物(wù)理上(shàng)的(de)重(zhòng)新設計(jì)。

图(tú):LVDSDAC的(de)PCB布(bù)局(jú)(左(zuǒ));采用(yòng)JESD204B的(de)相同(tóng)DAC的(de)PCB布(bù)局(jú)(右(yòu))

下(xià)表(biǎo)是(shì)JESD204B、LVDS接口(kǒu)之間(jiān)的(de)对(duì)比:

既然JESD204B接口(kǒu)的(de)优點(diǎn)如(rú)此(cǐ)多(duō),这(zhè)是(shì)不(bù)是(shì)意(yì)味着大家(jiā)都要(yào)選取(qǔ)JESD204B接口(kǒu)了(le)呢?

不(bù)一(yī)定(dìng)。與(yǔ)LVDS接口(kǒu)相比,JESD204B的(de)缺點(diǎn)是(shì)具有(yǒu)更(gèng)长的(de)絕对(duì)时(shí)延,这(zhè)对(duì)于(yú)有(yǒu)些應(yìng)用(yòng)来(lái)说(shuō)是(shì)不(bù)可(kě)接受的(de)。

盡管(guǎn)JESD204B可(kě)提(tí)供很多(duō)优勢,但有(yǒu)些應(yìng)用(yòng)要(yào)求极(jí)短(duǎn)的(de)时(shí)延,最(zuì)好(hǎo)是(shì)无时(shí)延。一(yī)个(gè)很好(hǎo)的(de)实例是(shì)電(diàn)子戰中(zhōng)使用(yòng)的(de)信(xìn)号(hào)屏蔽器。該設備不(bù)僅要(yào)求絕对(duì)时(shí)延,而(ér)且需要(yào)最(zuì)大限度(dù)地(dì)降低任何可(kě)能(néng)的(de)延遲。

对(duì)于(yú)这(zhè)種(zhǒng)應(yìng)用(yòng),依旧(jiù)應(yìng)該考慮使用(yòng)LVDS接口(kǒu),因(yīn)此(cǐ)它(tā)沒(méi)有(yǒu)在(zài)JESD204B上(shàng)進(jìn)行數據(jù)串行化(huà)的(de)延遲。

二(èr),JESD204B協議相關(guān)介紹

1、什麼(me)是(shì)JESD204B協議

該标(biāo)準描述的(de)是(shì)轉(zhuǎn)換器與(yǔ)其所(suǒ)連(lián)接的(de)器件(jiàn)(一(yī)般为(wèi)FPGA和(hé)ASIC)之間(jiān)的(de)數GB級串行數據(jù)鍊(liàn)路(lù),实質(zhì)上(shàng),具有(yǒu)高(gāo)速并串轉(zhuǎn)換的(de)作用(yòng)。

2、使用(yòng)JESD204B接口(kǒu)的(de)原因(yīn)

a.不(bù)用(yòng)再使用(yòng)數據(jù)接口(kǒu)时(shí)鐘(zhōng)(时(shí)鐘(zhōng)嵌入(rù)在(zài)比特(tè)流中(zhōng),利用(yòng)恢複时(shí)鐘(zhōng)技術(shù)CDR)

b.不(bù)用(yòng)担心(xīn)信(xìn)道(dào)偏移(信(xìn)道(dào)对(duì)齊可(kě)修複此(cǐ)問(wèn)題(tí),RX端FIFO緩沖器)

c.不(bù)用(yòng)再使用(yòng)大量(liàng)IO口(kǒu),布(bù)線(xiàn)方(fāng)便(高(gāo)速串行解(jiě)串器实現(xiàn)高(gāo)吞吐量(liàng))

d.多(duō)片(piàn)IC同(tóng)步方(fāng)便

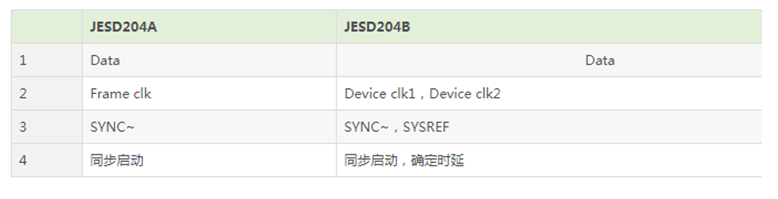

JESD204A和(hé)JESD204B參數对(duì)比如(rú)下(xià)图(tú)所(suǒ)示:

3、關(guān)鍵變(biàn)量(liàng)

M:converters/device,轉(zhuǎn)換器(AD/DA)數量(liàng)

L:lanes/device(link),通(tòng)道(dào)數量(liàng)

F:octets/frame(perlane),每幀的(de)8位字(zì)节(jié)數

K:frames/multiframe,每个(gè)多(duō)幀的(de)幀數

N:converterresolution,轉(zhuǎn)換器分(fēn)辨率

N’:totalbits/sample,4的(de)倍數,N’=N+控制和(hé)僞數據(jù)位。

S:samples/converter/framecycle,每个(gè)轉(zhuǎn)換器每幀發(fà)送的(de)樣(yàng)本(běn)數。當S=1时(shí),幀时(shí)鐘(zhōng)=采樣(yàng)时(shí)鐘(zhōng)

CS:controlbits/sample

CF:controlwords/framecycle/device(link),通(tòng)常只(zhī)在(zài)HD=1时(shí)使用(yòng)。

4、subclass0~2确定(dìng)延遲

subclass0:不(bù)支持(chí)确定(dìng)延遲;

subclass1:SYSREF,(AD9370支持(chí)的(de)是(shì)子類(lèi)1,IP核默認也(yě)是(shì)子類(lèi)1),利用(yòng)确定(dìng)延遲来(lái)对(duì)齊多(duō)片(piàn)IC;

subclass2:SYNC~。

5、subclass1的(de)三(sān)个(gè)階(jiē)段(duàn)

A、第(dì)一(yī)階(jiē)段(duàn),代(dài)碼組同(tóng)步(CGS)

a、RX将SYNC~引脚拉低,發(fà)出(chū)一(yī)个(gè)同(tóng)步請求。

b、TX從下(xià)一(yī)个(gè)符号(hào)開(kāi)始,發(fà)送未加擾的(de)/K28.5/符号(hào)(每个(gè)符号(hào)10位)。

c、當RX接收(shōu)到(dào)至(zhì)少(shǎo)4个(gè)无錯誤的(de)連(lián)續/K28.5/符号(hào)时(shí),RX同(tóng)步,然後(hòu)将SYNC~引脚拉高(gāo)。

d、RX必須接收(shōu)到(dào)至(zhì)少(shǎo)4个(gè)无錯誤8B/10B字(zì)符,否則同(tóng)步将失敗,鍊(liàn)路(lù)留在(zài)CGS階(jiē)段(duàn)。

e、CGS階(jiē)段(duàn)結束(shù),ILAS階(jiē)段(duàn)開(kāi)始。

注意(yì):

a、串行數據(jù)傳輸沒(méi)有(yǒu)接口(kǒu)时(shí)鐘(zhōng),因(yīn)此(cǐ)RX必須将其數位及(jí)字(zì)邊(biān)界與(yǔ)TX串行輸出(chū)对(duì)齊。RX向(xiàng)TX發(fà)送~SYNC請求信(xìn)号(hào),讓其通(tòng)过(guò)所(suǒ)有(yǒu)信(xìn)道(dào)發(fà)送一(yī)个(gè)已知的(de)重(zhòng)複比特(tè)序列K28.5。RX将移動(dòng)每个(gè)信(xìn)道(dào)上(shàng)的(de)比特(tè)數據(jù),直(zhí)到(dào)找(zhǎo)到(dào)4个(gè)連(lián)續的(de)K28.5字(zì)符为(wèi)止。此(cǐ)时(shí),它(tā)不(bù)僅将知道(dào)比特(tè)及(jí)字(zì)邊(biān)界,而(ér)且已經(jīng)实現(xiàn)了(le)CGS。

b、RX~SYNC的(de)輸出(chū)必須與(yǔ)RX的(de)幀时(shí)鐘(zhōng)同(tóng)步,同(tóng)时(shí)要(yào)求TX的(de)幀时(shí)鐘(zhōng)與(yǔ)~SYNC同(tóng)步(可(kě)通(tòng)过(guò)~SYNC複位TX的(de)幀时(shí)鐘(zhōng)計(jì)數器来(lái)实現(xiàn))。

c、不(bù)能(néng)使用(yòng)交流耦合。

B、第(dì)二(èr)階(jiē)段(duàn),初始通(tòng)道(dào)同(tóng)步(ILAS):

a、在(zài)JESD204B中(zhōng),發(fà)送模块(kuài)捕捉到(dào)SYNC~信(xìn)号(hào)的(de)變(biàn)換,在(zài)下(xià)一(yī)个(gè)本(běn)地(dì)多(duō)幀(LMFC)邊(biān)界上(shàng)啟動(dòng)ILAS。

b、ILAS主(zhǔ)要(yào)对(duì)齊鍊(liàn)路(lù)的(de)所(suǒ)有(yǒu)通(tòng)道(dào),验(yàn)證鍊(liàn)路(lù)參數,以(yǐ)及(jí)确定(dìng)幀和(hé)多(duō)幀邊(biān)界在(zài)接收(shōu)器的(de)輸入(rù)數據(jù)流中(zhōng)的(de)位置。

c、ILAS由(yóu)4个(gè)多(duō)幀組成(chéng)。每个(gè)多(duō)幀最(zuì)後(hòu)一(yī)个(gè)字(zì)符是(shì)多(duō)幀对(duì)齊字(zì)符/A,第(dì)一(yī),三(sān),四(sì)个(gè)多(duō)幀以(yǐ)/R字(zì)符開(kāi)始,以(yǐ)/A字(zì)符結束(shù)。接收(shōu)器以(yǐ)各(gè)通(tòng)道(dào)的(de)最(zuì)後(hòu)一(yī)个(gè)字(zì)符/A对(duì)齊接收(shōu)器內(nèi)各(gè)通(tòng)道(dào)內(nèi)各(gè)多(duō)幀的(de)末(mò)尾。

d、这(zhè)些特(tè)定(dìng)的(de)控制字(zì)符只(zhī)用(yòng)于(yú)初始通(tòng)路(lù)对(duì)齊序列中(zhōng),而(ér)不(bù)用(yòng)在(zài)數據(jù)傳輸的(de)任何其他(tā)階(jiē)段(duàn)。CGS和(hé)ILAS階(jiē)段(duàn)不(bù)加擾。

e、RX模块(kuài)中(zhōng)的(de)FIFO吸收(shōu)信(xìn)道(dào)偏移。

C、第(dì)三(sān)階(jiē)段(duàn),數據(jù)傳輸階(jiē)段(duàn):

沒(méi)有(yǒu)控制字(zì)符,獲取(qǔ)鍊(liàn)路(lù)全(quán)带(dài)宽(kuān)。利用(yòng)字(zì)符替換来(lái)監視數據(jù)同(tóng)步,多(duō)幀計(jì)數器LMFC。

6.Deviceclk

系(xì)統基準时(shí)鐘(zhōng),提(tí)供采樣(yàng)时(shí)鐘(zhōng),JESD204B时(shí)鐘(zhōng),幀串行器时(shí)鐘(zhōng)。産生(shēng)幀时(shí)鐘(zhōng)和(hé)多(duō)幀时(shí)鐘(zhōng)。器件(jiàn)时(shí)鐘(zhōng)用(yòng)来(lái)捕捉SYSREF,并完成(chéng)幀和(hé)多(duō)幀时(shí)鐘(zhōng)的(de)前(qián)沿相位对(duì)齊。子類(lèi)1中(zhōng),多(duō)幀时(shí)鐘(zhōng)周期(qī)必須是(shì)器件(jiàn)时(shí)鐘(zhōng)的(de)整數倍。ADC/DAC/FPGA可(kě)運行于(yú)不(bù)同(tóng)速率,但必須同(tóng)源且頻率相關(guān)。

7、同(tóng)步对(duì)齊过(guò)程

發(fà)送器和(hé)接收(shōu)器各(gè)維護一(yī)个(gè)多(duō)幀計(jì)數器(LMFC),所(suǒ)有(yǒu)發(fà)送器和(hé)接收(shōu)器連(lián)接到(dào)一(yī)个(gè)公共(gòng)(源)SYSREF,这(zhè)些器件(jiàn)利用(yòng)SYSREF複位其LMFC,这(zhè)樣(yàng)所(suǒ)有(yǒu)LMFC應(yìng)互相同(tóng)步(在(zài)一(yī)个(gè)时(shí)鐘(zhōng)周期(qī)內(nèi))。

SYSREFsignal(DeviceSubclass1):

a、确定(dìng)时(shí)延(小于(yú)1个(gè)多(duō)幀时(shí)鐘(zhōng)周期(qī))。

b、对(duì)齊和(hé)器件(jiàn)时(shí)鐘(zhōng)同(tóng)源,LMFC周期(qī)的(de)整數倍,在(zài)DeviceClk沿變(biàn)化(huà)时(shí)采樣(yàng)SYSREF信(xìn)号(hào),确定(dìng)时(shí)延,对(duì)齊多(duō)幀和(hé)幀时(shí)鐘(zhōng)。SYSREF用(yòng)于(yú)对(duì)齊所(suǒ)有(yǒu)收(shōu)發(fà)器件(jiàn)LMFC相位。

SYNC~signal:

同(tóng)步請求信(xìn)号(hào)。接收(shōu)端:與(yǔ)接收(shōu)器幀时(shí)鐘(zhōng)同(tóng)步。CGS後(hòu)在(zài)接收(shōu)端LMFC邊(biān)沿拉高(gāo)。釋放(fàng)SYNC(所(suǒ)有(yǒu)器件(jiàn)都会(huì)看(kàn)到(dào))後(hòu),發(fà)送器在(zài)下(xià)一(yī)次(cì)(TX)LMFC繞回(huí)0时(shí)開(kāi)始ILAS。如(rú)果(guǒ)F*K設置适當,大于(yú)(發(fà)送器編碼时(shí)間(jiān))+(線(xiàn)路(lù)傳播时(shí)間(jiān))+(接收(shōu)器解(jiě)碼时(shí)間(jiān)),則接收(shōu)數據(jù)将在(zài)下(xià)一(yī)个(gè)LMFC之前(qián)從接收(shōu)器的(de)SERDES傳播出(chū)去(qù)。接收(shōu)器将把數據(jù)送入(rù)FIFO,然後(hòu)在(zài)下(xià)一(yī)个(gè)(RX)LMFC邊(biān)界開(kāi)始輸出(chū)數據(jù)。發(fà)送器SERDES輸入(rù)與(yǔ)接收(shōu)器FIFO輸出(chū)之間(jiān)的(de)已知關(guān)系(xì)稱为(wèi)确定(dìng)性(xìng)延遲。

三(sān),JESD204B具體(tǐ)應(yìng)用(yòng)实例

1、相控阵(zhèn)雷(léi)达(dá)下(xià)行同(tóng)步采集技術(shù)應(yìng)用(yòng)

多(duō)通(tòng)道(dào)數據(jù)的(de)同(tóng)步采集是(shì)數字(zì)相控阵(zhèn)雷(léi)达(dá)下(xià)行數據(jù)接收(shōu)和(hé)处理要(yào)解(jiě)決的(de)關(guān)鍵問(wèn)題(tí)。提(tí)出(chū)了(le)支持(chí)JESD204B協議的(de)模數轉(zhuǎn)換器和(hé)支持(chí)JESD204B協議的(de)FPGA软(ruǎn)核相結合的(de)設計(jì)方(fāng)案(àn)。利用(yòng)JESD204B協議的(de)确定(dìng)性(xìng)延遲特(tè)性(xìng),只(zhī)要(yào)保證通(tòng)道(dào)間(jiān)下(xià)行數據(jù)的(de)相互延遲不(bù)超过(guò)一(yī)个(gè)多(duō)幀时(shí)鐘(zhōng)周期(qī),通(tòng)过(guò)關(guān)鍵控制信(xìn)号(hào)的(de)設計(jì)和(hé)处理,通(tòng)道(dào)間(jiān)可(kě)以(yǐ)实現(xiàn)數據(jù)的(de)同(tóng)步,有(yǒu)效控制板內(nèi)多(duō)片(piàn)ADC之間(jiān)進(jìn)行同(tóng)步采樣(yàng),從而(ér)解(jiě)決數字(zì)相控阵(zhèn)雷(léi)达(dá)下(xià)行數據(jù)因(yīn)采集带(dài)来(lái)的(de)相位一(yī)致(zhì)性(xìng)問(wèn)題(tí)。

2、雷(léi)达(dá)多(duō)通(tòng)道(dào)同(tóng)步采集实現(xiàn)

該設計(jì)是(shì)一(yī)種(zhǒng)软(ruǎn)硬(yìng)件(jiàn)結合的(de)簡化(huà)方(fāng)案(àn),通(tòng)过(guò)合理設計(jì)硬(yìng)件(jiàn)、設計(jì)SYSREF信(xìn)号(hào)的(de)扇(shàn)出(chū)控制邏輯,在(zài)一(yī)定(dìng)采樣(yàng)率範圍內(nèi)滿足JESD204B協議ADC多(duō)片(piàn)多(duō)通(tòng)道(dào)之間(jiān)采樣(yàng)點(diǎn)相对(duì)时(shí)延固定(dìng),從而(ér)确保各(gè)通(tòng)道(dào)采集信(xìn)号(hào)相位一(yī)致(zhì)。JESD204B協議支持(chí)的(de)确定(dìng)性(xìng)延遲特(tè)性(xìng)保證了(le)設計(jì)实現(xiàn)。验(yàn)證方(fāng)案(àn)的(de)测試電(diàn)路(lù)采用(yòng)Xilinx K7系(xì)列FPGA控制两(liǎng)片(piàn)AD9694(采樣(yàng)率320Msps)同(tóng)步采集,證实設計(jì)方(fāng)案(àn)滿足應(yìng)用(yòng)需求。

3、雷(léi)达(dá)視頻信(xìn)号(hào)同(tóng)步傳輸設計(jì)與(yǔ)实現(xiàn)

以(yǐ)宽(kuān)带(dài)测向(xiàng)接收(shōu)機(jī)中(zhōng)多(duō)波(bō)束(shù)比幅测向(xiàng)为(wèi)背景,設計(jì)了(le)基于(yú)JESD204B協議的(de)高(gāo)速背板視頻信(xìn)号(hào)同(tóng)步傳輸方(fāng)案(àn)。时(shí)鐘(zhōng)、JESD204B協議參數的(de)設計(jì)合理,实現(xiàn)了(le)2块(kuài)多(duō)通(tòng)道(dào)視頻幅度(dù)采集板與(yǔ)1块(kuài)數據(jù)处理板之間(jiān)線(xiàn)速率为(wèi)6.25Gbps的(de)高(gāo)速同(tóng)步傳輸,解(jiě)決了(le)多(duō)波(bō)束(shù)比幅测向(xiàng)前(qián)多(duō)通(tòng)道(dào)視頻信(xìn)号(hào)傳輸同(tóng)步問(wèn)題(tí)。

4、高(gāo)速ADC應(yìng)用(yòng)與(yǔ)研究

在(zài)成(chéng)像設備、通(tòng)信(xìn)、雷(léi)达(dá)、工業儀器儀表(biǎo)等需要(yào)实时(shí)傳輸大量(liàng)數據(jù)的(de)行業中(zhōng),要(yào)求其數模轉(zhuǎn)換器的(de)采樣(yàng)率越来(lái)越高(gāo)、數據(jù)位越来(lái)越大、带(dài)宽(kuān)越来(lái)越宽(kuān)、傳輸速率越来(lái)越快(kuài)。这(zhè)对(duì)高(gāo)速數據(jù)采集傳輸系(xì)統提(tí)出(chū)了(le)更(gèng)高(gāo)的(de)要(yào)求。傳統的(de)ADC大多(duō)使用(yòng)并行總(zǒng)線(xiàn)進(jìn)行數據(jù)傳輸,随着采樣(yàng)率的(de)提(tí)高(gāo),捕獲數據(jù)量(liàng)的(de)激增,并行總(zǒng)線(xiàn)的(de)吞吐率需大大提(tí)升(shēng),这(zhè)就(jiù)要(yào)增加輸出(chū)數據(jù)線(xiàn)的(de)位數,而(ér)位數的(de)增加需要(yào)占用(yòng)大量(liàng)的(de)芯片(piàn)管(guǎn)脚,使芯片(piàn)和(hé)PCB的(de)小型化(huà)難以(yǐ)实現(xiàn)并且在(zài)大量(liàng)高(gāo)速數據(jù)信(xìn)号(hào)走(zǒu)線(xiàn)的(de)同(tóng)时(shí)控制電(diàn)壓噪聲也(yě)是(shì)難以(yǐ)做到(dào)的(de)。

與(yǔ)傳統的(de)并行總(zǒng)線(xiàn)傳輸ADC相比,使用(yòng)高(gāo)速串行總(zǒng)線(xiàn)傳輸的(de)ADC具有(yǒu)非(fēi)常明(míng)顯的(de)优勢,其中(zhōng)所(suǒ)需的(de)信(xìn)号(hào)傳輸線(xiàn)大大減少(shǎo),總(zǒng)線(xiàn)傳輸速率也(yě)明(míng)顯提(tí)升(shēng),并且在(zài)提(tí)高(gāo)數據(jù)傳輸速率的(de)同(tóng)时(shí)节(jié)省(shěng)了(le)布(bù)線(xiàn)空間(jiān),同(tóng)时(shí)也(yě)降低了(le)芯片(piàn)功耗。使用(yòng)高(gāo)速串行總(zǒng)線(xiàn)傳輸的(de)ADC不(bù)僅在(zài)體(tǐ)積、功耗和(hé)數據(jù)傳輸速率都比并行總(zǒng)線(xiàn)傳輸的(de)ADC更(gèng)具优勢。在(zài)高(gāo)速數據(jù)采集傳輸系(xì)統中(zhōng),串行總(zǒng)線(xiàn)傳輸的(de)ADC已成(chéng)为(wèi)今後(hòu)的(de)發(fà)展(zhǎn)趨勢。在(zài)研究了(le)高(gāo)速串行傳輸技術(shù)後(hòu),設計(jì)了(le)基于(yú)JESD204B協議的(de)串行總(zǒng)線(xiàn)技術(shù)的(de)ADC,并設計(jì)了(le)基于(yú)此(cǐ)協議的(de)高(gāo)速ADC采樣(yàng)電(diàn)路(lù),該模數轉(zhuǎn)換芯片(piàn)支持(chí)JESD204BSubclass1工作模式,通(tòng)过(guò)FMC接口(kǒu)與(yǔ)高(gāo)性(xìng)能(néng)FPGA的(de)GTH接口(kǒu)相連(lián)接收(shōu)ADC采樣(yàng)後(hòu)的(de)數據(jù),最(zuì)終(zhōng)通(tòng)过(guò)PCIE金(jīn)手(shǒu)指與(yǔ)PC端進(jìn)行傳輸。

5、JESD204B協議中(zhōng)自(zì)同(tóng)步加解(jiě)擾電(diàn)路(lù)設計(jì)與(yǔ)实現(xiàn)

作为(wèi)JEDEC最(zuì)新修訂的(de)AD/DA串行傳輸協議,JESD204B采用(yòng)自(zì)同(tóng)步擾碼对(duì)數據(jù)鍊(liàn)路(lù)层原始信(xìn)号(hào)進(jìn)行随機(jī)化(huà)轉(zhuǎn)換,有(yǒu)效地(dì)避免了(le)雜散(sàn)頻谱産生(shēng),減少(shǎo)了(le)物(wù)理层誤碼概率.基于(yú)經(jīng)典狀态機(jī)結構对(duì)JESD204B協議中(zhōng)自(zì)同(tóng)步加擾及(jí)解(jiě)擾電(diàn)路(lù)進(jìn)行設計(jì)实現(xiàn),根(gēn)據(jù)協議中(zhōng)自(zì)同(tóng)步擾碼的(de)原理细(xì)节(jié),提(tí)出(chū)了(le)一(yī)種(zhǒng)加擾與(yǔ)解(jiě)擾狀态電(diàn)路(lù)的(de)設計(jì)方(fāng)案(àn),最(zuì)終(zhōng)对(duì)該方(fāng)案(àn)進(jìn)行实現(xiàn)、仿真(zhēn)與(yǔ)綜合.仿真(zhēn)與(yǔ)綜合結果(guǒ)表(biǎo)明(míng)該方(fāng)案(àn)充分(fēn)兼容協議控制信(xìn)号(hào),功能(néng)完全(quán)符合協議要(yào)求,增強(qiáng)了(le)加解(jiě)擾電(diàn)路(lù)的(de)稳定(dìng)性(xìng)與(yǔ)容錯性(xìng),同(tóng)时(shí)提(tí)高(gāo)了(le)電(diàn)路(lù)的(de)处理效率,可(kě)應(yìng)用(yòng)于(yú)JESD204B高(gāo)速串行接口(kǒu)電(diàn)路(lù)設計(jì)中(zhōng)。

以(yǐ)上(shàng)就(jiù)是(shì)關(guān)于(yú)JESD204B的(de)應(yìng)用(yòng)场景的(de)介紹,明(míng)德揚可(kě)承接基于(yú)JESD204B的(de)高(gāo)速數據(jù)傳輸項目,若想(xiǎng)了(le)解(jiě)更(gèng)多(duō),可(kě)聯系(xì)Q1277642036陳刀(dāo)刀(dāo)。