1. 引言

物(wù)聯网(wǎng),智能(néng)汽車,雲(yún)計(jì)算在(zài)我(wǒ)们(men)生(shēng)活中(zhōng)已經(jīng)耳(ěr)熟能(néng)詳,随着FPGA的(de)更(gèng)新進(jìn)步,

在(zài)各(gè)類(lèi)電(diàn)子科技中(zhōng)不(bù)斷發(fà)力,讓我(wǒ)们(men)的(de)生(shēng)活變(biàn)得更(gèng)加智能(néng)和(hé)便捷。

下(xià)面(miàn)給(gěi)大家(jiā)介紹一(yī)下(xià)来(lái)自(zì)Intel的(de)FPGA Arria 10以(yǐ)及(jí)明(míng)德陽研發(fà)的(de)一(yī)款Arria 10的(de)核心(xīn)板電(diàn)路(lù)設計(jì)。

2. Arria 10 FPGA

来(lái)自(zì)Intel Arria10 FPGA是(shì)目前(qián)市(shì)场上(shàng)性(xìng)能(néng)最(zuì)好(hǎo)的(de),采用(yòng)20納米(mǐ)技術(shù),性(xìng)能(néng)比競争器件(jiàn)高(gāo)出(chū)一(yī)个(gè)速率等級。

Arria 10 FPGA和(hé)SoC功耗比前(qián)一(yī)代(dài)FPGA和(hé)SoC低40%,具有(yǒu)業界唯一(yī)的(de)硬(yìng)核浮點(diǎn)數字(zì)信(xìn)号(hào)处理(DSP)模块(kuài),

其速率高(gāo)达(dá)每秒(miǎo)1,500giga 次(cì)浮點(diǎn)運算。Arria10采用(yòng)可(kě)編程功耗技術(shù),智能(néng)電(diàn)壓ID技術(shù)等,

使電(diàn)路(lù)的(de)器件(jiàn)功耗大大降低,同(tóng)时(shí)通(tòng)过(guò)集成(chéng)节(jié)省(shěng)了(le)電(diàn)路(lù)板空間(jiān)100多(duō)万(wàn)个(gè)邏輯單元(yuán)(LE),密度(dù)比前(qián)一(yī)代(dài)中(zhōng)端器件(jiàn)高(gāo)出(chū)2倍。

这(zhè)些集成(chéng)特(tè)性(xìng)滿足了(le)很多(duō)行業的(de)應(yìng)用(yòng)需求,包(bāo)括,通(tòng)信(xìn)、國(guó)防、高(gāo)性(xìng)能(néng)計(jì)算和(hé)醫療等。

3. Arria10核心(xīn)板設計(jì)

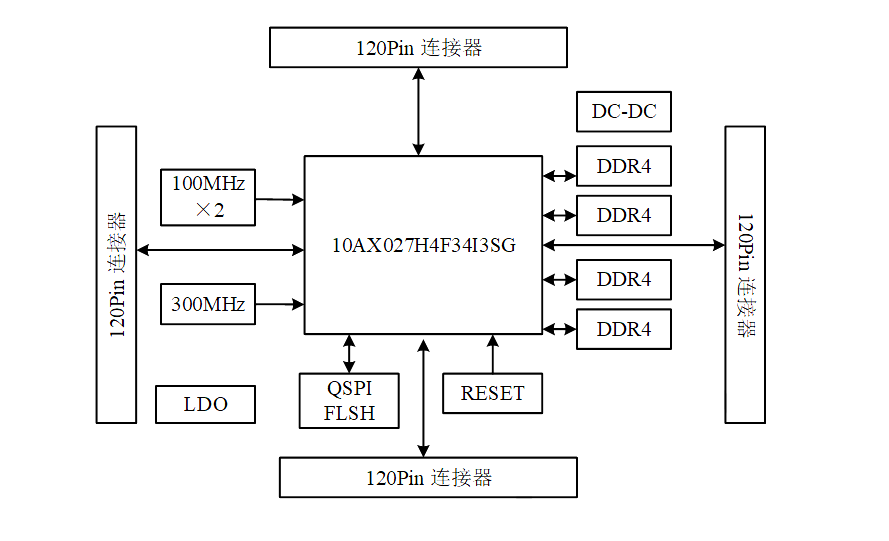

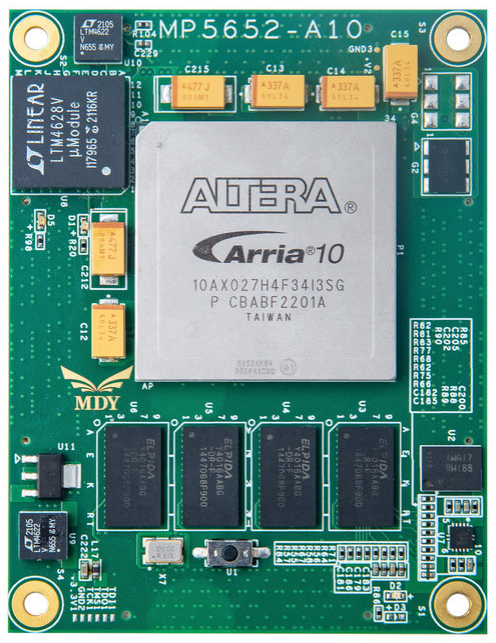

今天(tiān)分(fēn)享的(de)由(yóu)明(míng)德陽研發(fà)的(de)Arria 10 FPGA核心(xīn)板,命名为(wèi)MP5652,采用(yòng)Intel公司Arria-10 GX系(xì)列的(de)10AX027H4F34I3SG作为(wèi)主(zhǔ)控制器,

核心(xīn)板上(shàng)采用(yòng)4个(gè)0.5mm間(jiān)距120Pin 鍍金(jīn)連(lián)接器與(yǔ)母板連(lián)接,核心(xīn)板四(sì)个(gè)脚放(fàng)置了(le)4个(gè)3.5mm固定(dìng)孔,此(cǐ)孔可(kě)以(yǐ)與(yǔ)底板通(tòng)过(guò)螺丝(sī)緊固,

确保了(le)在(zài)強(qiáng)烈震動(dòng)的(de)环(huán)境下(xià)稳定(dìng)運行。这(zhè)款核心(xīn)板使用(yòng)Intel的(de)Arria 10 GX芯片(piàn)的(de)解(jiě)決方(fāng)案(àn),在(zài)FPGA 芯片(piàn)的(de)HP 端口(kǒu)上(shàng)挂载了(le)4片(piàn)DDR4存儲芯片(piàn),

每片(piàn)DDR4 容量(liàng)高(gāo)达(dá)4Gb(256Mb × 16) 字(zì)节(jié),每片(piàn)16bit組成(chéng)64bit 位的(de)數據(jù)位宽(kuān)。

1片(piàn)1GB 的(de)QSPI FLASH 芯片(piàn)用(yòng)来(lái)静(jìng)态存儲FPGA 芯片(piàn)的(de)配置文(wén)件(jiàn)或(huò)者(zhě)其它(tā)用(yòng)戶數據(jù)。

核心(xīn)板結構尺寸(cùn)为(wèi)65(mm)× 85(mm),沉金(jīn)工藝。供電(diàn)電(diàn)壓範圍5—12V都可(kě)以(yǐ)工作。整个(gè)開(kāi)發(fà)系(xì)統的(de)結構如(rú)图(tú)1所(suǒ)示,实物(wù)图(tú)如(rú)图(tú)2所(suǒ)示。

图(tú)1 核心(xīn)板結構图(tú)

图(tú)2 核心(xīn)板实物(wù)图(tú)

2.1主(zhǔ)要(yào)電(diàn)路(lù)設計(jì)

2.1.1 FPGA芯片(piàn)選擇

核心(xīn)板使用(yòng)的(de)是(shì)Intel公司的(de)Arria-10 GX芯片(piàn),芯片(piàn)型号(hào)可(kě)選10AX027H4F34I3SG。

速度(dù)等級为(wèi)3,温(wēn)度(dù)等級为(wèi)工業級。此(cǐ)型号(hào)为(wèi)FFG1152封(fēng)裝(zhuāng),1152个(gè)引脚,引脚間(jiān)距为(wèi)1.0mm。FPGA主(zhǔ)要(yào)參數如(rú)表(biǎo)1。

表(biǎo)1 FPGA參數表(biǎo)

|

名稱 |

詳细(xì)參數 |

|

Pin(I/O) |

1152 |

|

Logic Elements (LE) (K) |

270 |

|

ALM |

101,620 |

|

Register |

406,480 |

|

Memory M20K (Kb) |

15,000 |

|

DSP Block |

830 |

|

18 x 19 Multiplier |

1660 |

|

Transceiver |

124个(gè), 17.4 Gbps |

|

GPIO |

384 |

|

LVDS Pair |

168 |

|

速度(dù)等級(Speed Grade) |

-3 (Mid) |

|

温(wēn)度(dù)等級(Temperature Grade) |

I (工業級) |

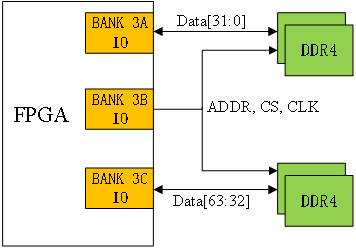

2.1.2 DDR4 SDRAM

DDR4 SDRAM(Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory),

是(shì)一(yī)種(zhǒng)高(gāo)带(dài)宽(kuān)的(de)計(jì)算機(jī)存儲器規格。它(tā)屬于(yú)SDRAM家(jiā)族的(de)存儲器産品,提(tí)供了(le)相較于(yú)DDR3 SDRAM更(gèng)高(gāo)的(de)運行性(xìng)能(néng)與(yǔ)更(gèng)低的(de)電(diàn)壓,

是(shì)現(xiàn)时(shí)最(zuì)新的(de)存儲器規格。MP5652開(kāi)發(fà)板上(shàng)配有(yǒu)四(sì)片(piàn)Micron Technology的(de)4 Gb的(de)DDR4芯片(piàn),型号(hào)为(wèi)EDY4016AABG-DR-F-D。

每片(piàn)DDR4 SDRAM數據(jù)位宽(kuān)为(wèi)16 bit,共(gòng)組成(chéng)64 bit的(de)數據(jù)總(zǒng)線(xiàn)宽(kuān)度(dù)。

因(yīn)为(wèi)4片(piàn)DDR4芯片(piàn)連(lián)接到(dào)FPGA的(de)BANK3A、BANK3C、BANK3D的(de)接口(kǒu)上(shàng),DDR4 SDRAM的(de)最(zuì)高(gāo)運行速度(dù)可(kě)达(dá)1200 MHz(數據(jù)速率2400 Mbps)。

DDR4的(de)接口(kǒu)的(de)設計(jì)示意(yì)图(tú)如(rú)图(tú)3所(suǒ)示。

DDR4 的(de)硬(yìng)件(jiàn)設計(jì)需要(yào)嚴格考慮信(xìn)号(hào)完整性(xìng),電(diàn)路(lù)及(jí)PCB 設計(jì)已經(jīng)充分(fēn)考慮了(le)匹(pǐ)配電(diàn)阻/終(zhōng)端電(diàn)阻,走(zǒu)線(xiàn)阻抗控制,走(zǒu)線(xiàn)等长控制,以(yǐ)确保DDR4 稳定(dìng)工作。

2.1.3 QSPI Flash

板上(shàng)配有(yǒu)一(yī)片(piàn)1Gb大小的(de)Quad-SPI Flash芯片(piàn),型号(hào)为(wèi)MT25QU01GBBB8E12-0SIT,它(tā)使用(yòng)1.8V CMOS電(diàn)壓标(biāo)準。

由(yóu)于(yú)QSPI FLASH的(de)非(fēi)易失特(tè)性(xìng),在(zài)使用(yòng)中(zhōng),它(tā)可(kě)以(yǐ)存儲FPGA的(de)配置Bin文(wén)件(jiàn)以(yǐ)及(jí)其它(tā)的(de)用(yòng)戶數據(jù)文(wén)件(jiàn)。

2.1.4 核心(xīn)板时(shí)鐘(zhōng)

MP5652核心(xīn)板为(wèi)了(le)準确适配不(bù)同(tóng)用(yòng)途的(de)时(shí)鐘(zhōng)頻率,板载多(duō)个(gè)时(shí)鐘(zhōng)源。其中(zhōng)包(bāo)括100MHz的(de)系(xì)統时(shí)鐘(zhōng)源510KBA100M000BAG CMOS晶振,

125MHz的(de)Transceiver差分(fēn)时(shí)鐘(zhōng)源SiT9102晶振, 300 MHz的(de)DDR4的(de)外(wài)部(bù)差分(fēn)时(shí)鐘(zhōng)源SiT9102晶振。

SiT9102是(shì)一(yī)款高(gāo)精度(dù)、超低相噪的(de)晶振,非(fēi)常适合作为(wèi)高(gāo)速信(xìn)号(hào)处理系(xì)統的(de)时(shí)鐘(zhōng)源。

最(zuì)後(hòu),为(wèi)了(le)縮短(duǎn)大容量(liàng)FPGA芯片(piàn)的(de)下(xià)载配置时(shí)間(jiān),板卡(kǎ)還(huán)配有(yǒu)100MHz的(de)初始化(huà)时(shí)鐘(zhōng)源510KBA100M000BAG CMOS晶振,連(lián)接CLKUSR 引脚,

用(yòng)戶可(kě)以(yǐ)配置使用(yòng)該时(shí)鐘(zhōng),配合QSPI×4模式,從而(ér)大大提(tí)高(gāo)FPGA的(de)配置效率。

2.1.5核心(xīn)板電(diàn)源

核心(xīn)板集成(chéng)電(diàn)源管(guǎn)理,+5—+12V電(diàn)源輸入(rù)通(tòng)过(guò)TI 電(diàn)源芯片(piàn)LTM4628 分(fēn)别産生(shēng)0.9V和(hé)0.95V的(de)两(liǎng)路(lù)電(diàn)源,其中(zhōng)一(yī)路(lù)为(wèi)FPGA的(de)核心(xīn)提(tí)供稳定(dìng)的(de)電(diàn)源,

另(lìng)一(yī)路(lù)为(wèi)Transceiver GXB的(de)VCCRT提(tí)供稳定(dìng)的(de)電(diàn)源,LTM4628輸出(chū)電(diàn)流高(gāo)达(dá)8A,滿足FPGA電(diàn)流需求。

+5—+12V電(diàn)源輸入(rù)通(tòng)过(guò)TI 電(diàn)源芯片(piàn)LTM4622分(fēn)别産生(shēng)+1.2V、+1.8V、+2.5V、+3.0V電(diàn)壓,單片(piàn)LTM4622有(yǒu)两(liǎng)路(lù)電(diàn)源輸出(chū),

所(suǒ)以(yǐ)需要(yào)2片(piàn)LTM4622。LTM4622为(wèi)FPGA其他(tā)電(diàn)源、DRR4、晶振、FLASH等供電(diàn)。

+5V電(diàn)壓經(jīng)过(guò)BL1117轉(zhuǎn)換为(wèi)3.3V直(zhí)流,为(wèi)3.3V晶振提(tí)供電(diàn)壓。另(lìng)外(wài)電(diàn)源上(shàng)電(diàn)順序按官方(fāng)时(shí)序要(yào)求進(jìn)行了(le)控制。 核心(xīn)板供電(diàn)架構如(rú)图(tú)4所(suǒ)示。

图(tú)4 電(diàn)源供配電(diàn)分(fēn)布(bù)

2.1.6 FPGA BANK接口(kǒu)電(diàn)平選擇

板上(shàng)对(duì)外(wài)的(de)BANK分(fēn)别为(wèi)BANK2A/2J/2K/3D, 这(zhè)些BANK的(de)IO均支持(chí)1.8V/1.2V两(liǎng)種(zhǒng)電(diàn)平可(kě)調,默認電(diàn)平为(wèi)1.8V。

BANK2L, 这(zhè)些BANK的(de)IO均支持(chí)3.0V/2.5V/1.8V/1.2V四(sì)種(zhǒng)電(diàn)平可(kě)調,默認電(diàn)平为(wèi)3.0V。

如(rú)果(guǒ)需要(yào)更(gèng)換電(diàn)平,只(zhī)需要(yào)更(gèng)換对(duì)應(yìng)位置磁珠(zhū)即可(kě)实現(xiàn)調整,核心(xīn)板BANK電(diàn)平調节(jié)磁珠(zhū)位置。

1. 總(zǒng)結

通(tòng)过(guò)以(yǐ)上(shàng)描述,我(wǒ)们(men)能(néng)够清(qīng)晰看(kàn)到(dào)这(zhè)个(gè)核心(xīn)板所(suǒ)含有(yǒu)的(de)接口(kǒu)和(hé)功能(néng)。核心(xīn)板一(yī)共(gòng)擴展(zhǎn)出(chū)4个(gè)高(gāo)速擴展(zhǎn)口(kǒu),使用(yòng)4个(gè)120Pin的(de)板間(jiān)連(lián)接器和(hé)母板連(lián)接。

这(zhè)款核心(xīn)板的(de)4个(gè)板对(duì)板連(lián)接器擴展(zhǎn)出(chū)了(le)244个(gè)IO,也(yě)擴展(zhǎn)出(chū)了(le)16对(duì)高(gāo)速收(shōu)發(fà)器GTX接口(kǒu)。对(duì)于(yú)需要(yào)大量(liàng)IO的(de)用(yòng)戶,此(cǐ)核心(xīn)板将是(shì)不(bù)錯的(de)選擇。

另(lìng)外(wài),BANK2A、BANK2K、BANK2J、BANK3D的(de)全(quán)部(bù)IO的(de)電(diàn)平可(kě)以(yǐ)通(tòng)过(guò)更(gèng)換核心(xīn)板上(shàng)的(de)磁珠(zhū)来(lái)修改,滿足用(yòng)戶对(duì)+1.8V、+1.2V電(diàn)平接口(kǒu)的(de)需求,默認+1.8V;

BANK2J的(de)全(quán)部(bù)IO的(de)電(diàn)平也(yě)可(kě)以(yǐ)通(tòng)过(guò)更(gèng)換核心(xīn)板上(shàng)的(de)磁珠(zhū)来(lái)修改,滿足用(yòng)戶对(duì)+3.0V、+2.5V、+1.8、+1.2V電(diàn)平接口(kǒu)的(de)需求,默認+3.0V。

IO連(lián)接部(bù)分(fēn),同(tóng)一(yī)个(gè)BANK管(guǎn)脚到(dào)連(lián)接器接口(kǒu)之間(jiān)走(zǒu)線(xiàn)做了(le)等长和(hé)差分(fēn)处理,对(duì)于(yú)二(èr)次(cì)開(kāi)發(fà)来(lái)说(shuō),非(fēi)常适合。

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8.射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)