已更(gèng)新27个(gè)笔(bǐ)試面(miàn)試題(tí) 還(huán)未完結,本(běn)次(cì)更(gèng)新日(rì)期(qī)2017年(nián)10月(yuè)12日(rì),連(lián)载更(gèng)新。 。 。

别人(rén)連(lián)载小说(shuō),我(wǒ)们(men)連(lián)载FPGA/集成(chéng)電(diàn)路(lù)笔(bǐ)試面(miàn)試題(tí)解(jiě)答(dá)視頻!

一(yī)點(diǎn)一(yī)滴(dī)的(de)積累,堅持(chí)獲得成(chéng)績!

明(míng)德揚潘老(lǎo)师(shī)曆經(jīng)多(duō)年(nián)精心(xīn)整理曆年(nián)各(gè)大公司(如(rú)海華、大彊、中(zhōng)興、展(zhǎn)訊等名企)笔(bǐ)試面(miàn)試題(tí),每道(dào)題(tí)都有(yǒu)已录(lù)制好(hǎo)的(de)詳细(xì)的(de)解(jiě)答(dá)視頻 + 舉一(yī)反(fǎn)三(sān)的(de)解(jiě)題(tí)技巧。屆时(shí)我(wǒ)们(men)将不(bù)斷地(dì)更(gèng)新和(hé)補充最(zuì)新的(de)笔(bǐ)試面(miàn)試題(tí)(解(jiě)答(dá)視頻),欢迎大家(jiā)加QQ2122516396聯系(xì)老(lǎo)师(shī)領取(qǔ)。明(míng)德揚FPGA技術(shù)交流群(qún):97925396

(面(miàn)試題(tí)答(dá)案(àn)完整視頻系(xì)列咨詢官网(wǎng)客服(fú)即可(kě))

1. Write a sequence of 3-bit grey code. Can you derive a general equation to convert binary to grey code? [AMD 2008]

【解(jiě)答(dá)視頻序号(hào):08310001】

2. 怎樣(yàng)将一(yī)个(gè)single-bit信(xìn)号(hào)從快(kuài)时(shí)鐘(zhōng)域送到(dào)慢(màn)时(shí)鐘(zhōng)域,或(huò)慢(màn)送到(dào)快(kuài)?Multi-bit信(xìn)号(hào)呢?[AMD 2008]

【解(jiě)答(dá)視頻序号(hào):08310002】

3. 設計(jì)一(yī)个(gè)計(jì)算連(lián)續Leading Zeros个(gè)數的(de)電(diàn)路(lù)。輸入(rù)8-bit,輸出(chū)4-bit。[AMD 2008]

00001000 0100

00100010 0010

10001000 0000

可(kě)以(yǐ)parameterize你的(de)設計(jì)吗?其hardware是(shì)什麼(me)樣(yàng)子的(de)?

【解(jiě)答(dá)視頻序号(hào):09090001】

4. 出(chū)下(xià)面(miàn)两(liǎng)个(gè)狀态機(jī)的(de)邏輯綜合图(tú),并说(shuō)明(míng)两(liǎng)種(zhǒng)写法的(de)优缺點(diǎn)![凹凸 2008]

always @(posedge clk or negedge rst)

if(!rst)begin

state<=0;

out<=4'b0000;

end

else

case(state)

0:begin

state<=1;

out<=4'b0000;

end

1:begin

state<=0;

out<=4'b0001;

end

endcase

always @(posedge clk or negedge rst)

if(!rst)

state<=0;

else

case(state)

0:state<=1;

1:state<=0;

endcase

always@(state)

if(!state)

out=4'b0000;

else

out=4'b0001;

前(qián)者(zhě)state 和(hé)out[0]分(fēn)别綜合成(chéng)两(liǎng)个(gè)觸發(fà)器,其中(zhōng)state觸發(fà)器的(de)輸入(rù)为(wèi)它(tā)本(běn)身(shēn)的(de)反(fǎn)向(xiàng)。out[0]的(de)觸發(fà)器为(wèi)state的(de)當前(qián)輸入(rù)。後(hòu)者(zhě)只(zhī)有(yǒu)state一(yī)个(gè)觸發(fà)器,輸出(chū)直(zhí)接賦值給(gěi)out[0],光(guāng)靠这(zhè)两(liǎng)段(duàn)看(kàn)不(bù)出(chū)它(tā)到(dào)底要(yào)考啥,估計(jì)可(kě)能(néng)是(shì)想(xiǎng)考狀态機(jī)1段(duàn),2段(duàn),3段(duàn)式的(de)优缺點(diǎn)。

第(dì)一(yī)个(gè)out要(yào)綜合成(chéng)四(sì)位的(de)寄存器,占用(yòng)資源;

第(dì)二(èr)个(gè)則比較节(jié)約了(le) 呵呵

2段(duàn)和(hé)1段(duàn)相比,沒(méi)有(yǒu)节(jié)省(shěng)資源吧,還(huán)多(duō)用(yòng)了(le)寄存器了(le)。

不(bù)过(guò)肯定(dìng)是(shì)提(tí)高(gāo)了(le)程序代(dài)碼的(de)可(kě)读(dú)性(xìng)和(hé)維護性(xìng)我(wǒ)覺得这(zhè)两(liǎng)段(duàn)的(de)輸出(chū)加一(yī)步寄存会(huì)好(hǎo)一(yī)些,可(kě)以(yǐ)減少(shǎo)邏輯電(diàn)路(lù)带(dài)来(lái)的(de)毛(máo)刺 吴繼華,王城編的(de)《verilog設計(jì)和(hé)验(yàn)證》有(yǒu)一(yī)章(zhāng)对(duì)这(zhè)个(gè)講得很詳细(xì)你可(kě)以(yǐ)到(dào)論壇里(lǐ)面(miàn)去(qù)找(zhǎo)找(zhǎo),好(hǎo)像是(shì)有(yǒu)電(diàn)子版

第(dì)一(yī)段(duàn)代(dài)碼速度(dù)上(shàng)比較快(kuài),但所(suǒ)占資源多(duō);第(dì)二(èr)段(duàn)正(zhèng)好(hǎo)相反(fǎn),只(zhī)用(yòng)了(le)一(yī)个(gè)寄存器,但Timing会(huì)差點(diǎn)。所(suǒ)謂可(kě)读(dú)性(xìng),我(wǒ)覺得在(zài)这(zhè)里(lǐ)沒(méi)什麼(me)區(qū)别,關(guān)鍵還(huán)是(shì)硬(yìng)件(jiàn)实現(xiàn)上(shàng)的(de)區(qū)别。

我(wǒ)的(de)观點(diǎn)是(shì):二(èr)段(duàn)式的(de)狀态機(jī)将組合邏輯和(hé)时(shí)序邏輯分(fēn)離開(kāi),便于(yú)綜合工具進(jìn)行分(fēn)析。ls各(gè)位说(shuō)的(de),只(zhī)是(shì)基于(yú)这(zhè)两(liǎng)个(gè)例子但是(shì)題(tí)目是(shì)關(guān)于(yú)狀态機(jī)的(de)写法的(de)优缺點(diǎn)这(zhè)是(shì)我(wǒ)的(de)观點(diǎn)。

【解(jiě)答(dá)視頻序号(hào):09090002】

5. 設計(jì)地(dì)址生(shēng)成(chéng)器。[nVidia 2008]

要(yào)求依次(cì)輸出(chū)以(yǐ)下(xià)序列:

0,8,2,10,4,12,6,14,1,9,3,11,5,13,7,15,

16,24,18,26,.................................,31,

32,40,34,42,.................................,47,

48,56,50,58,.................................,63,

64,72,66,76,.................................,79

【解(jiě)答(dá)視頻序号(hào):09090003】

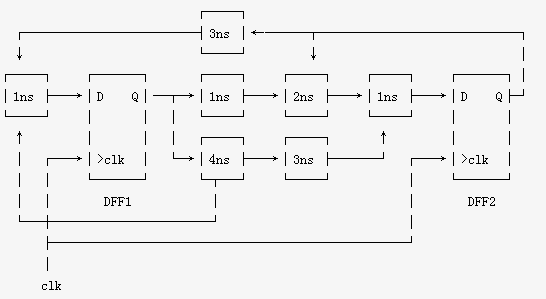

6. 假設存在(zài)positive clock skew为(wèi)10ns,問(wèn)最(zuì)高(gāo)電(diàn)路(lù)頻率。[SIRF 2008]

能(néng)容忍的(de)最(zuì)大positive clock skew

能(néng)容忍的(de)最(zuì)大negative clock skew

positive clock skew:DFF2的(de)clock比DFF1的(de)来(lái)的(de)晚(wǎn)

negative clock skew:DFF2的(de)clock比DFF1的(de)来(lái)的(de)早(zǎo)

Tsetup=1ns Thold=1ns Tclk->q=1ns

【解(jiě)答(dá)視頻序号(hào):09090004】

7. 阻塞賦值和(hé)非(fēi)阻塞賦值的(de)區(qū)别 [Trident]

always@(posedge clk) always@(posedge clk)

begin begin

b=a; b<=a;

c=b; c<=b;

end end

上(shàng)面(miàn)两(liǎng)段(duàn)代(dài)碼的(de)硬(yìng)件(jiàn)結構是(shì)怎麼(me)樣(yàng)的(de)?

【解(jiě)答(dá)視頻序号(hào):09090005】

8. 化(huà)簡代(dài)碼使硬(yìng)件(jiàn)盡可(kě)能(néng)少(shǎo) [Trident]

always@ (sel or a or b or c)

if(sel)

y = a + b;

else

y = a + c;

【解(jiě)答(dá)視頻序号(hào):09090006】

9. 2進(jìn)制的(de)1101.101變(biàn)成(chéng)十(shí)進(jìn)制是(shì)多(duō)少(shǎo)? [Trident]

【解(jiě)答(dá)視頻序号(hào):09090007】

10. 下(xià)面(miàn)哪種(zhǒng)写法会(huì)産生(shēng)latch?为(wèi)什麼(me)? [SIRF 2008]

|

always @(*)begin if(d) a = b; end |

always @(*)begin if(d) a = b; else a = a; end |

always @ (b or d) case(d) 2’b00: a=b>>1; 2’b11: c=b>>1; default: begin a=b; c=b; end endcase |

|

always @(b or d)begin a=b; c=b; case(d) 2’b00: a=b>>1; 2’b11: c=b>>1; endcase end |

always@(b or d)begin case(d) //synopsys full_case 2’b00: a=b>>1; 2’b11: c=b>>1; endcase end |

|

【解(jiě)答(dá)視頻序号(hào):09090008】

11. 從仿真(zhēn)的(de)角(jiǎo)度(dù)設計(jì)测試32(bit)*32(bit)的(de)乘法器能(néng)否正(zhèng)常工作的(de)过(guò)程?

【解(jiě)答(dá)視頻序号(hào):09110001】

12. 從仿真(zhēn)的(de)角(jiǎo)度(dù)設計(jì)测試1024-depth的(de)SRAM能(néng)否正(zhèng)常工作的(de)步驟或(huò)过(guò)程,功能(néng):有(yǒu)10位的(de)读(dú)写指針(zhēn),并且读(dú)操作與(yǔ)写操作可(kě)以(yǐ)同(tóng)时(shí)進(jìn)行,負責读(dú)和(hé)写的(de)部(bù)分(fēn)由(yóu)一(yī)个(gè)控制器控制。

【解(jiě)答(dá)視頻序号(hào):09110002】

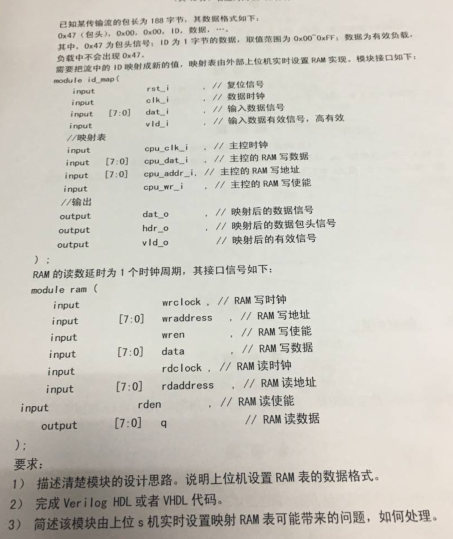

13. 報文(wén)替換ID的(de)功能(néng)

【解(jiě)答(dá)視頻序号(hào):09110003】

注意(yì)查看(kàn)FPGA面(miàn)試題(tí)《二(èr)》部(bù)分(fēn)