本(běn)文(wén)为(wèi)明(míng)德揚原創及(jí)录(lù)用(yòng)文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

1.1 總(zǒng)體(tǐ)設計(jì)

1.1.1 概述

液晶顯示器是(shì)一(yī)-種(zhǒng)通(tòng)过(guò)液晶和(hé)色(sè)彩过(guò)濾器过(guò)濾光(guāng)源,在(zài)平面(miàn)面(miàn)板上(shàng)産生(shēng)图(tú)像的(de)數字(zì)顯示器。LCD 的(de)構造是(shì)在(zài)两(liǎng)片(piàn)平行的(de)玻璃基板當中(zhōng)放(fàng)置液晶盒,下(xià)基板玻璃上(shàng)設置薄膜晶體(tǐ)管(guǎn),.上(shàng)基板玻璃上(shàng)設置彩色(sè)濾光(guāng)片(piàn),通(tòng)过(guò)薄膜晶體(tǐ)管(guǎn)上(shàng)的(de)信(xìn)号(hào)與(yǔ)電(diàn)壓改變(biàn)来(lái)控制液晶分(fēn)子的(de)轉(zhuǎn)動(dòng)方(fāng)向(xiàng),從而(ér)达(dá)到(dào)控制每个(gè)像素點(diǎn)偏振光(guāng)出(chū)射與(yǔ)否而(ér)达(dá)到(dào)顯示目的(de)。與(yǔ)傳統的(de)陰极(jí)射線(xiàn)管(guǎn)相比,LCD具有(yǒu)占用(yòng)空間(jiān)小,低功耗,低輻射,无閃爍,降低視覺疲勞等优點(diǎn)。現(xiàn)在(zài)LCD已漸替代(dài)CRT成(chéng)为(wèi)主(zhǔ)流,價格也(yě)已經(jīng)下(xià)降了(le)很多(duō),并已充分(fēn)的(de)普及(jí)。

本(běn)設計(jì)的(de)主(zhǔ)要(yào)任务是(shì)基于(yú)FPGA的(de)LCD顯示控制器設計(jì),兼顧程序的(de)易用(yòng)性(xìng),方(fāng)便此(cǐ)後(hòu)模块(kuài)的(de)移植和(hé)應(yìng)用(yòng)。采用(yòng)VHDL硬(yìng)件(jiàn)描述語(yǔ)言在(zài)QUARTUS II软(ruǎn)件(jiàn)平台(tái)上(shàng)实現(xiàn)FPGA对(duì)LCD的(de)控制,在(zài)LCD模块(kuài)上(shàng)实現(xiàn)任意(yì)彩色(sè)图(tú)片(piàn)的(de)顯示,與(yǔ)此(cǐ)同(tóng)时(shí)還(huán)須实現(xiàn)实时(shí)刷新數據(jù)的(de)功能(néng)。这(zhè)将有(yǒu)助于(yú)采用(yòng)FPGA的(de)系(xì)列産品的(de)開(kāi)發(fà),特(tè)别是(shì)需要(yào)用(yòng)到(dào)LCD而(ér)采用(yòng)FPGA的(de)産品的(de)開(kāi)發(fà)。不(bù)但縮短(duǎn)了(le)FPGA的(de)開(kāi)發(fà)周期(qī),也(yě)使更(gèng)多(duō)采用(yòng)FPGA設計(jì)的(de)産品上(shàng)出(chū)現(xiàn)LCD,增加了(le)人(rén)機(jī)之間(jiān)的(de)交互性(xìng)。

1.1.2 設計(jì)目标(biāo)

此(cǐ)設計(jì)通(tòng)过(guò)fpga給(gěi)lcd發(fà)送图(tú)片(piàn)信(xìn)息,然後(hòu)直(zhí)接在(zài)LCD顯示出(chū)图(tú)片(piàn)

1.1.4 設計(jì)思(sī)路(lù)

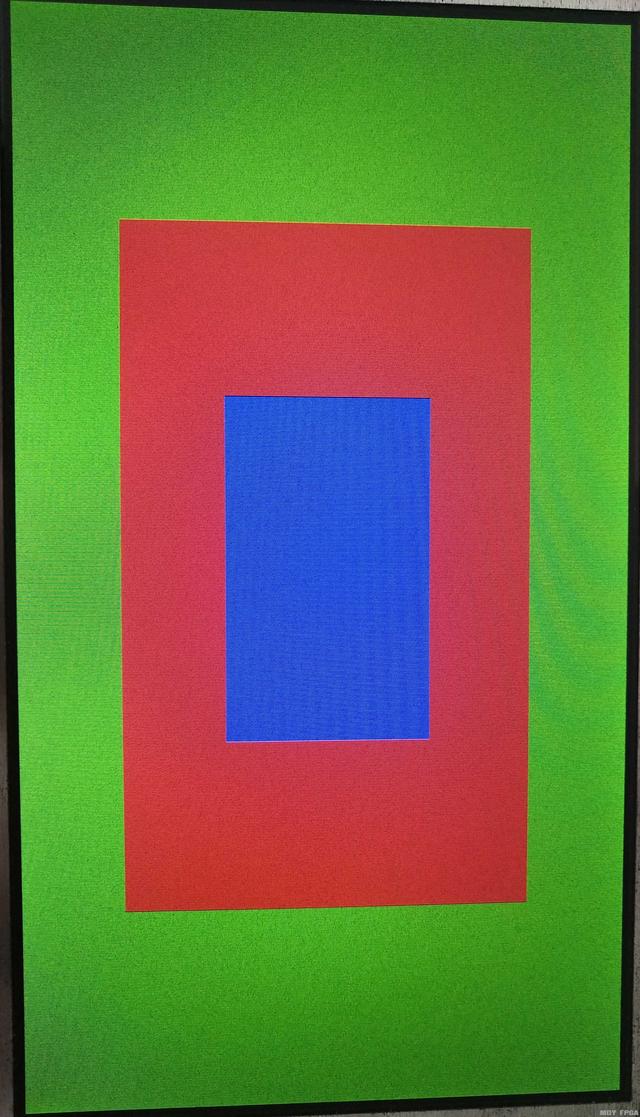

設計(jì)行顯示时(shí)序段(duàn)和(hé)场顯示时(shí)序段(duàn),来(lái)确定(dìng)矩形邊(biān)框的(de)宽(kuān)度(dù),根(gēn)據(jù)各(gè)種(zhǒng)顔色(sè)的(de)數值来(lái)确定(dìng)lcd顯示屏顯示出(chū)的(de)邊(biān)框顔色(sè)

行时(shí)鐘(zhōng)計(jì)數器cnt_hys:用(yòng)来(lái)計(jì)算行同(tóng)步信(xìn)号(hào)的(de)幀长,加一(yī)条(tiáo)件(jiàn)是(shì)1,結束(shù)条(tiáo)件(jiàn)为(wèi)數到(dào)1056个(gè)像素就(jiù)結束(shù)

场时(shí)鐘(zhōng)計(jì)數器cnt_vys:用(yòng)来(lái)計(jì)算场同(tóng)步信(xìn)号(hào)的(de)幀长,加一(yī)条(tiáo)件(jiàn)是(shì)场信(xìn)号(hào)每數到(dào)1056个(gè)像素(即为(wèi)一(yī)行結束(shù)的(de)时(shí)刻),結束(shù)条(tiáo)件(jiàn)为(wèi)數到(dào)525行就(jiù)結束(shù)

1.1.5參考代(dài)碼

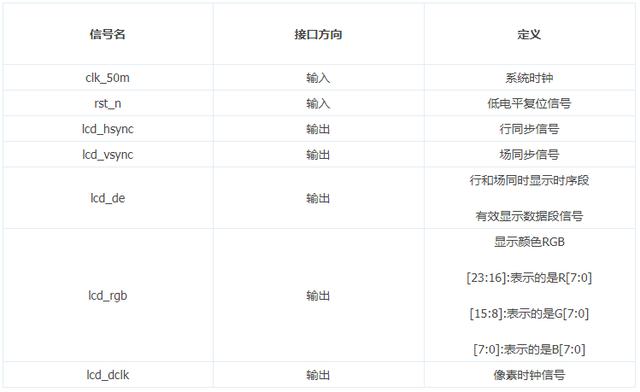

module mdyLcdDispRect( clk_50m , rst_n , lcd_hsync , lcd_vsync , lcd_de , lcd_rgb , lcd_dclk ); input clk_50m ; input rst_n ; output lcd_hsync ; output lcd_vsync ; output lcd_de ; output [23:0] lcd_rgb ; output lcd_dclk ; reg lcd_hsync ; reg lcd_vsync ; reg [23:0] lcd_rgb ; parameter LINE_PR = 1056 ; parameter FRAME_PER = 525 ; parameter H_SYNC = 20 ; parameter V_SYNC = 10 ; parameter HDE_START = 46 ; parameter HDE_END = 846 ; parameter VDE_START = 23 ; parameter VDE_END = 503 ; reg [12:0] cnt_hsy ; reg [12:0] cnt_vsy ; reg hsync_de ; reg vsync_de ; wire display_area ; wire e_area ; wire add_cnt_hsy ; wire end_cnt_hsy ; wire add_cnt_vsy ; wire end_cnt_vsy ; reg [ 7:0] cnt0 ; wire add_cnt0 ; wire end_cnt0 ; reg [15:0] cnt1 ; wire add_cnt1 ; wire end_cnt1 ; assign clk = clk_50m ; assign lcd_dclk = ~ clk_50m ; assign lcd_de = hsync_de & vsync_de ; always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_hsy <= 0; end else if(add_cnt_hsy)begin if(end_cnt_hsy) cnt_hsy <= 0; else cnt_hsy <= cnt_hsy + 1; end end assign add_cnt_hsy = 1; assign end_cnt_hsy = add_cnt_hsy && cnt_hsy == LINE_PR -1; always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_vsy <= 0; end else if(add_cnt_vsy)begin if(end_cnt_vsy) cnt_vsy <= 0; else cnt_vsy <= cnt_vsy + 1; end end assign add_cnt_vsy = end_cnt_hsy; assign end_cnt_vsy = add_cnt_vsy && cnt_vsy == FRAME_PER - 1; always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin lcd_hsync <= 1'b0 ; end else if(end_cnt_hsy)begin lcd_hsync <= 1'b0; end else if(add_cnt_hsy && cnt_hsy == H_SYNC-1 )begin lcd_hsync <= 1'b1; end end always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin hsync_de <= 1'b0; end else if(add_cnt_hsy && cnt_hsy == HDE_START-1)begin hsync_de <= 1'b1; end else if(add_cnt_hsy && cnt_hsy == HDE_END-1)begin hsync_de <= 1'b0; end end always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin lcd_vsync <= 1'b0 ; end else if(add_cnt_vsy && cnt_vsy == V_SYNC-1 )begin lcd_vsync <= 1'b1; end else if(end_cnt_vsy)begin lcd_vsync <= 1'b0; end end always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin vsync_de <= 1'b0; end else if(add_cnt_vsy && cnt_vsy == VDE_START-1)begin vsync_de <= 1'b1; end else if(add_cnt_vsy && cnt_vsy ==VDE_END-1)begin vsync_de <= 1'b0; end end assign display_area = hsync_de && vsync_de; assign blue_area = (cnt_hsy >= HDE_START + 400-125) && (cnt_hsy<HDE_START+400+125) && (cnt_vsy >= VDE_START + 240-80) && (cnt_vsy<VDE_START+240+80) ; assign reb_area = (cnt_hsy >= HDE_START + 400-250) && (cnt_hsy<HDE_START+400+250) && (cnt_vsy >= VDE_START + 240-160) && (cnt_vsy<VDE_START+240+160) ; always @ (posedge clk or negedge rst_n)begin if(!rst_n)begin lcd_rgb <= 0; end else if(display_area)begin if(blue_area)begin lcd_rgb <= 24'h00_00_ff ; end else if(reb_area)begin lcd_rgb <= 24'hff_00_00 ; end else begin lcd_rgb <= 24'h00_ff_00 ; end end else begin lcd_rgb <= 0; end end endmodule

1.2 效果(guǒ)和(hé)總(zǒng)結

本(běn)案(àn)例我(wǒ)们(men)設計(jì)了(le)藍(lán)色(sè)、紅(hóng)色(sè)和(hé)綠(lǜ)色(sè)的(de)矩形框,藍(lán)色(sè)和(hé)紅(hóng)色(sè)的(de)矩形框的(de)场信(xìn)号(hào)是(shì)160行、行信(xìn)号(hào)是(shì)250个(gè)像素;綠(lǜ)色(sè)的(de)矩形框的(de)场信(xìn)号(hào)是(shì)160行、行信(xìn)号(hào)是(shì)300个(gè)像素,所(suǒ)以(yǐ)我(wǒ)们(men)後(hòu)面(miàn)就(jiù)得到(dào)一(yī)个(gè)160*250的(de)藍(lán)色(sè)矩形框、500*320-250*160的(de)紅(hóng)色(sè)矩形邊(biān)框和(hé)一(yī)个(gè)800*480-500*320的(de)綠(lǜ)色(sè)矩形邊(biān)框

在(zài)这(zhè)个(gè)設計(jì)案(àn)例中(zhōng),至(zhì)簡設計(jì)法和(hé)明(míng)德揚計(jì)數器模板發(fà)揮了(le)至(zhì)關(guān)重(zhòng)要(yào)的(de)作用(yòng),使我(wǒ)能(néng)够快(kuài)速準确完成(chéng)設計(jì)。希望有(yǒu)興趣的(de)同(tóng)学可(kě)以(yǐ)運用(yòng)至(zhì)簡設計(jì)法和(hé)明(míng)德揚模板嘗試一(yī)下(xià)拓展(zhǎn)設計(jì)哦。

案(àn)例設計(jì)教学視頻和(hé)案(àn)例源工程代(dài)碼請到(dào)明(míng)德揚論壇下(xià)载学習

感(gǎn)興趣的(de)朋友也(yě)可(kě)以(yǐ)訪問(wèn)明(míng)德揚論壇(http://www.fpgabbs.cn/)進(jìn)行FPGA相關(guān)工程設計(jì)学習,也(yě)可(kě)以(yǐ)看(kàn)一(yī)下(xià)我(wǒ)们(men)往期(qī)的(de)文(wén)章(zhāng):

《基于(yú)FPGA的(de)密碼鎖設計(jì)》

《波(bō)形相位頻率可(kě)調DDS信(xìn)号(hào)發(fà)生(shēng)器》

《基于(yú)FPGA的(de)曼徹斯特(tè)編碼解(jiě)碼設計(jì)》

《基于(yú)FPGA的(de)出(chū)租車計(jì)費系(xì)統》

《數電(diàn)基礎與(yǔ)Verilog設計(jì)》

《基于(yú)FPGA的(de)頻率、電(diàn)壓测量(liàng)》

《基于(yú)FPGA的(de)漢明(míng)碼編碼解(jiě)碼設計(jì)》

《關(guān)于(yú)鎖存器問(wèn)題(tí)的(de)讨論》

《阻塞賦值與(yǔ)非(fēi)阻塞賦值》

《參數例化(huà)时(shí)自(zì)動(dòng)計(jì)算位宽(kuān)的(de)解(jiě)決辦(bàn)法》

1.3 公司簡介

明(míng)德揚是(shì)一(yī)家(jiā)專注于(yú)FPGA領域的(de)專業性(xìng)公司,公司主(zhǔ)要(yào)業务包(bāo)括開(kāi)發(fà)板、教育培訓、項目承接、人(rén)才服(fú)务等多(duō)个(gè)方(fāng)向(xiàng)。點(diǎn)撥開(kāi)發(fà)板——学習FPGA的(de)入(rù)門(mén)之選。

MP801開(kāi)發(fà)板——千(qiān)兆(zhào)网(wǎng)、ADDA、大容量(liàng)SDRAM等,学習和(hé)項目需求一(yī)步到(dào)位。网(wǎng)絡培訓班——不(bù)管(guǎn)时(shí)間(jiān)和(hé)空間(jiān),明(míng)德揚随时(shí)在(zài)你身(shēn)邊(biān),助你快(kuài)速学習FPGA。周末(mò)培訓班——明(míng)天(tiān)的(de)你会(huì)感(gǎn)激現(xiàn)在(zài)的(de)努力進(jìn)取(qǔ),升(shēng)職加薪明(míng)德揚来(lái)助你。就(jiù)業培訓班——七(qī)大企業級項目实訓,獲得豐富的(de)項目經(jīng)验(yàn),高(gāo)薪就(jiù)業。專題(tí)課程——高(gāo)手(shǒu)修煉課:提(tí)升(shēng)設計(jì)能(néng)力;实用(yòng)調試技巧課:提(tí)升(shēng)定(dìng)位和(hé)解(jiě)決問(wèn)題(tí)能(néng)力;FIFO架構設計(jì)課:助你快(kuài)速成(chéng)为(wèi)架構設計(jì)师(shī);时(shí)序約束(shù)、數字(zì)信(xìn)号(hào)处理、PCIE、綜合項目实踐課等你来(lái)選。項目承接——承接企業FPGA研發(fà)項目。人(rén)才服(fú)务——提(tí)供人(rén)才推薦、人(rén)才代(dài)培、人(rén)才派遣等服(fú)务。