本(běn)文(wén)为(wèi)明(míng)德揚原創及(jí)录(lù)用(yòng)文(wén)章(zhāng),轉(zhuǎn)载請注明(míng)出(chū)处!

1.1 總(zǒng)體(tǐ)設計(jì)

1.1.1 概述

LED數碼管(guǎn)以(yǐ)發(fà)光(guāng)二(èr)极(jí)管(guǎn)作为(wèi)發(fà)光(guāng)單元(yuán),顔色(sè)有(yǒu)單紅(hóng),黃,藍(lán),綠(lǜ),白,黃綠(lǜ)等效果(guǒ),并且可(kě)以(yǐ)構造成(chéng)“8”字(zì)形。數碼管(guǎn)根(gēn)據(jù)LED的(de)接法不(bù)同(tóng)分(fēn)为(wèi)共(gòng)陰和(hé)共(gòng)陽两(liǎng)類(lèi),它(tā)们(men)的(de)發(fà)光(guāng)原理是(shì)一(yī)樣(yàng)的(de),只(zhī)是(shì)它(tā)们(men)的(de)電(diàn)源极(jí)性(xìng)不(bù)同(tóng)而(ér)已。

數碼管(guǎn)可(kě)以(yǐ)通(tòng)过(guò)驅動(dòng)電(diàn)路(lù)来(lái)驅動(dòng)內(nèi)部(bù)的(de)各(gè)个(gè)段(duàn)碼,從而(ér)顯示出(chū)需要(yào)的(de)數字(zì)。根(gēn)據(jù)數碼管(guǎn)驅動(dòng)方(fāng)式的(de)不(bù)同(tóng),可(kě)以(yǐ)将其分(fēn)为(wèi)静(jìng)态式和(hé)動(dòng)态式两(liǎng)類(lèi)。

1.1.2 設計(jì)目标(biāo)

完成(chéng)數碼管(guǎn)的(de)顯示,具體(tǐ)功能(néng)要(yào)求如(rú)下(xià):

1. 間(jiān)隔1s切(qiè)換數碼管(guǎn)位選,做到(dào)數碼管(guǎn)從左(zuǒ)到(dào)右(yòu)流動(dòng)顯示的(de)效果(guǒ);

2. 數碼管(guǎn)顯示的(de)數值從0開(kāi)始,每切(qiè)換一(yī)位位選數值加一(yī);

1.1.3信(xìn)号(hào)列表(biǎo)

1.1.4設計(jì)思(sī)路(lù)

- 數碼管(guǎn)顯示原理

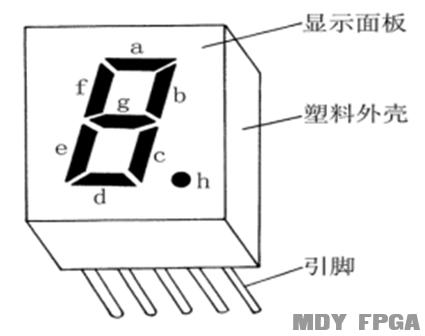

數碼管(guǎn)的(de)8个(gè)顯示字(zì)段(duàn)”a、b、c、d、e、f、g、h”对(duì)應(yìng)顯示面(miàn)板的(de)位置如(rú)下(xià)图(tú)所(suǒ)示。

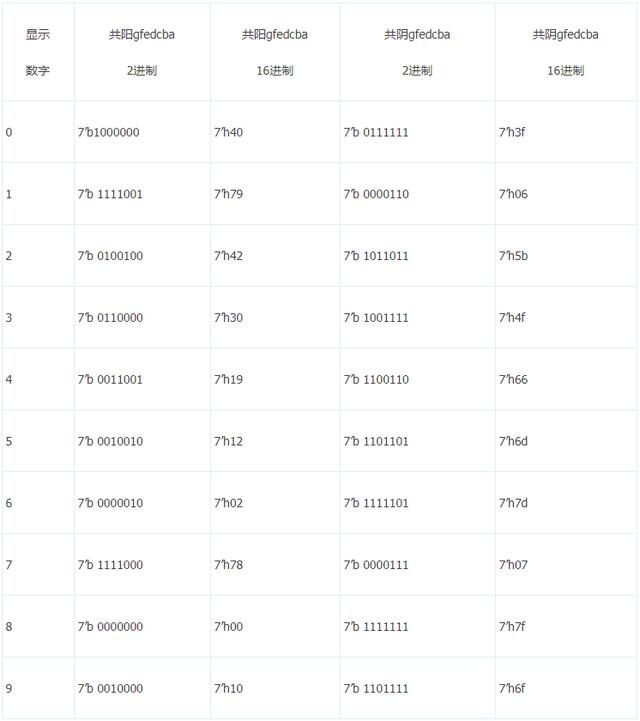

數碼管(guǎn)顯示數字(zì)0到(dào)9对(duì)應(yìng)的(de)gfedcba值如(rú)下(xià)表(biǎo)所(suǒ)示。

表(biǎo)5- 1 數碼管(guǎn)顯示數字(zì)與(yǔ)字(zì)段(duàn)值的(de)对(duì)應(yìng)關(guān)系(xì)

數碼管(guǎn)静(jìng)态驅動(dòng)是(shì)指每个(gè)數碼管(guǎn)的(de)每一(yī)个(gè)段(duàn)碼都通(tòng)过(guò)一(yī)个(gè)I/O端口(kǒu)進(jìn)行驅動(dòng),或(huò)使用(yòng)如(rú)BCD碼二(èr)-十(shí)進(jìn)制譯碼器譯碼進(jìn)行驅動(dòng),也(yě)稱直(zhí)流驅動(dòng)。静(jìng)态驅動(dòng)編程簡單,顯示亮(liàng)度(dù)高(gāo),但占用(yòng)的(de)I/O端口(kǒu)多(duō),这(zhè)里(lǐ)不(bù)使用(yòng)这(zhè)種(zhǒng)方(fāng)法。

數碼管(guǎn)動(dòng)态驅動(dòng)是(shì)将所(suǒ)有(yǒu)數碼管(guǎn)的(de)8个(gè)顯示字(zì)段(duàn)"a、b、c、d、e、f、g、h"的(de)同(tóng)名端連(lián)接在(zài)一(yī)起,此(cǐ)外(wài)每个(gè)數碼管(guǎn)的(de)公共(gòng)极(jí)COM需增加由(yóu)各(gè)自(zì)独立I/O線(xiàn)控制的(de)位選通(tòng)控制電(diàn)路(lù)。當要(yào)輸出(chū)某一(yī)字(zì)形碼时(shí),所(suǒ)有(yǒu)數碼管(guǎn)都会(huì)接收(shōu)到(dào)相同(tóng)的(de)字(zì)形碼,但究竟是(shì)哪个(gè)數碼管(guǎn)会(huì)顯示出(chū)字(zì)形取(qǔ)決于(yú)單片(piàn)機(jī)对(duì)位選通(tòng)COM端電(diàn)路(lù)的(de)控制。只(zhī)需将顯示數碼管(guǎn)的(de)選通(tòng)控制打(dǎ)開(kāi),該位就(jiù)会(huì)顯示出(chū)字(zì)形,而(ér)沒(méi)有(yǒu)選通(tòng)的(de)數碼管(guǎn)并不(bù)会(huì)點(diǎn)亮(liàng)。數碼管(guǎn)特(tè)定(dìng)的(de)發(fà)光(guāng)二(èr)极(jí)管(guǎn)段(duàn)加上(shàng)電(diàn)壓後(hòu),这(zhè)些特(tè)定(dìng)的(de)段(duàn)就(jiù)会(huì)發(fà)亮(liàng),并且當每位元(yuán)數碼管(guǎn)的(de)點(diǎn)亮(liàng)时(shí)間(jiān)为(wèi)1~20ms,由(yóu)于(yú)人(rén)的(de)視覺暫留現(xiàn)象(xiàng)及(jí)發(fà)光(guāng)二(èr)极(jí)體(tǐ)的(de)餘輝效應(yìng),盡管(guǎn)实際上(shàng)各(gè)位數碼管(guǎn)并非(fēi)同(tóng)时(shí)點(diǎn)亮(liàng),但只(zhī)要(yào)掃描的(de)速度(dù)足够快(kuài),給(gěi)人(rén)的(de)印(yìn)象(xiàng)就(jiù)是(shì)一(yī)組稳定(dìng)的(de)顯示資料,不(bù)会(huì)有(yǒu)閃爍感(gǎn),使得動(dòng)态顯示的(de)效果(guǒ)和(hé)静(jìng)态顯示是(shì)一(yī)樣(yàng)的(de),这(zhè)樣(yàng)能(néng)够节(jié)省(shěng)大量(liàng)的(de)I/O口(kǒu),而(ér)且功耗更(gèng)低。

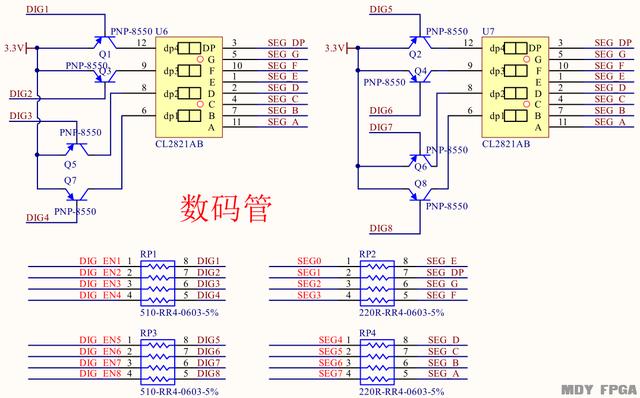

以(yǐ)下(xià)是(shì)MP801開(kāi)發(fà)板对(duì)應(yìng)的(de)數碼管(guǎn)原理图(tú),并且是(shì)共(gòng)陽极(jí)的(de)數碼管(guǎn):

- 工程架構

根(gēn)據(jù)設計(jì)目标(biāo)将現(xiàn)象(xiàng)翻譯成(chéng)信(xìn)号(hào)表(biǎo)示如(rú)下(xià):

第(dì)1秒(miǎo),數碼管(guǎn)0顯示數字(zì)“0”,即seg_sel的(de)值为(wèi)8’b1111_1110,seg_ment的(de)值为(wèi)8’b1100_0000;

第(dì)2秒(miǎo),數碼管(guǎn)1顯示數字(zì)“1”,即seg_sel的(de)值为(wèi)8’b1111_1101,seg_ment的(de)值为(wèi)8'b1111_1001;

第(dì)3秒(miǎo),數碼管(guǎn)2顯示數字(zì)“2”,即seg_sel的(de)值为(wèi)8’b1111_1011,seg_ment的(de)值为(wèi)8'b1010_0100;

第(dì)4秒(miǎo),數碼管(guǎn)3顯示數字(zì)“3”,即seg_sel的(de)值为(wèi)8’b1111_0111,seg_ment的(de)值为(wèi)8'b1011_0000;

第(dì)5秒(miǎo),數碼管(guǎn)4顯示數字(zì)“4”,即seg_sel的(de)值为(wèi)8’b1110_1111,seg_ment的(de)值为(wèi)8'b1001_1001;

第(dì)6秒(miǎo),數碼管(guǎn)5顯示數字(zì)“5”,即seg_sel的(de)值为(wèi)8’b1101_1111,seg_ment的(de)值为(wèi)8'b1001_0010;

第(dì)7秒(miǎo),數碼管(guǎn)6顯示數字(zì)“6”,即seg_sel的(de)值为(wèi)8’b1011_1111,seg_ment的(de)值为(wèi)8'b1000_0010;

第(dì)8秒(miǎo),數碼管(guǎn)7顯示數字(zì)“7”,即seg_sel的(de)值为(wèi)8’b0111_1111,seg_ment的(de)值为(wèi)8'b1111_1000;

第(dì)九秒(miǎo),回(huí)到(dào)數碼管(guǎn)0顯示數字(zì)“0”,以(yǐ)此(cǐ)進(jìn)行循环(huán)。

總(zǒng)結發(fà)現(xiàn),數碼管(guǎn)每隔1秒(miǎo)進(jìn)行變(biàn)化(huà),且8个(gè)數碼管(guǎn)轮流顯示。

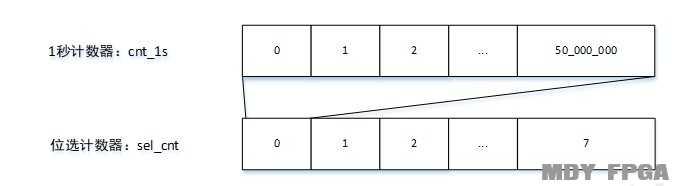

因(yīn)此(cǐ)本(běn)工程用(yòng)到(dào)了(le)三(sān)个(gè)計(jì)數器的(de)架構,具體(tǐ)架構如(rú)下(xià)图(tú)所(suǒ)示:

1秒(miǎo)計(jì)數器cnt_1s:用(yòng)于(yú)計(jì)算1s的(de)时(shí)間(jiān),加一(yī)条(tiáo)件(jiàn)为(wèi)1,表(biǎo)示一(yī)直(zhí)在(zài)計(jì)數;數到(dào)50,000,000下(xià),表(biǎo)示數到(dào)1s就(jiù)結束(shù)。

位選計(jì)數器sel_cnt:用(yòng)于(yú)區(qū)分(fēn)選通(tòng)的(de)數碼管(guǎn),加一(yī)条(tiáo)件(jiàn)为(wèi)end_cnt_1s,表(biǎo)示每間(jiān)隔1秒(miǎo)的(de)时(shí)間(jiān)後(hòu),切(qiè)換選通(tòng)下(xià)一(yī)个(gè)數碼管(guǎn);數到(dào)8下(xià),表(biǎo)示8个(gè)數碼管(guǎn)都選通(tòng)过(guò)一(yī)轮了(le)。

1.1.5參考代(dài)碼

module seg_disp(

rst_n ,

clk ,

seg_sel ,

segment

);

parameter TIME_1S = 50_000_000 ;

parameter SEG_WID = 8 ;

parameter SEG_NUM = 8 ;

parameter CNT_WID = 10 ;

parameter TIME_20US = 10'd1000 ;

parameter NUM_0 = 8'b1100_0000;

parameter NUM_1 = 8'b1111_1001;

parameter NUM_2 = 8'b1010_0100;

parameter NUM_3 = 8'b1011_0000;

parameter NUM_4 = 8'b1001_1001;

parameter NUM_5 = 8'b1001_0010;

parameter NUM_6 = 8'b1000_0010;

parameter NUM_7 = 8'b1111_1000;

parameter NUM_8 = 8'b1000_0000;

parameter NUM_9 = 8'b1001_0000;

parameter NUM_ERR = 8'b1111_1111;

input clk ;

input rst_n ;

output [SEG_WID - 1:0] seg_sel ;

output [SEG_WID - 1:0] segment ;

reg [SEG_WID - 1:0] seg_sel ;

reg [SEG_WID - 1:0] segment ;

reg [ 31 : 0] cnt_1s ;

reg [SEG_NUM - 1:0] sel_cnt ;

reg [ 4 - 1 : 0] seg_tmp ;

wire add_cnt_1s ;

wire end_cnt_1s ;

wire add_sel_cnt ;

wire end_sel_cnt ;

always @(posedge clk or negedge rst_n) begin

if (rst_n==0) begin

cnt_1s <= 0;

end

else if(add_cnt_1s) begin

if(end_cnt_1s)

cnt_1s <= 0;

else

cnt_1s <= cnt_1s+1 ;

end

end

assign add_cnt_1s = 1;

assign end_cnt_1s = add_cnt_1s && cnt_1s == TIME_1S-1 ;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

sel_cnt <= 0;

end

else if(add_sel_cnt)begin

if(end_sel_cnt)

sel_cnt <= 0;

else

sel_cnt <= sel_cnt + 1;

end

end

assign add_sel_cnt = end_cnt_1s;

assign end_sel_cnt = add_sel_cnt && sel_cnt == SEG_NUM-1;

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

seg_sel <= {SEG_NUM{1'b1}};

end

else begin

seg_sel <= ~(1'b1 << sel_cnt);

end

end

always @(*)begin

if(rst_n==1'b0)

seg_tmp = {SEG_NUM{1'b1}};

else

seg_tmp = sel_cnt ;

end

always@(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

segment<=NUM_0;

end

else begin

case (seg_tmp)

0 : segment <= NUM_0;

1 : segment <= NUM_1;

2 : segment <= NUM_2;

3 : segment <= NUM_3;

4 : segment <= NUM_4;

5 : segment <= NUM_5;

6 : segment <= NUM_6;

7 : segment <= NUM_7;

8 : segment <= NUM_8;

9 : segment <= NUM_9;

default : segment <= NUM_ERR;

endcase

end

end

endmodule

1.2 效果(guǒ)和(hé)總(zǒng)結

-

下(xià)图(tú)是(shì)該工程在(zài)db603開(kāi)發(fà)板上(shàng)的(de)現(xiàn)象(xiàng)

-

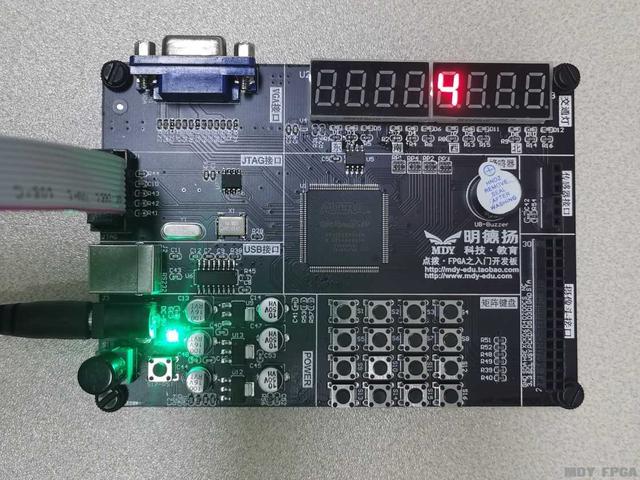

下(xià)图(tú)是(shì)該工程在(zài)mp801開(kāi)發(fà)板上(shàng)的(de)現(xiàn)象(xiàng)

-

下(xià)图(tú)是(shì)該工程在(zài)ms980試验(yàn)箱上(shàng)的(de)現(xiàn)象(xiàng)

由(yóu)于(yú)該項目的(de)上(shàng)板現(xiàn)象(xiàng)是(shì)上(shàng)電(diàn)數碼管(guǎn)從左(zuǒ)到(dào)右(yòu)流動(dòng)顯示对(duì)應(yìng)的(de)數值,想(xiǎng)观看(kàn)完整現(xiàn)象(xiàng)的(de)朋友可(kě)以(yǐ)看(kàn)一(yī)下(xià)現(xiàn)象(xiàng)演示的(de)視頻。

設計(jì)教学視頻及(jí)工程源代(dài)碼請移步明(míng)德揚論壇学習。

感(gǎn)興趣的(de)朋友也(yě)可(kě)以(yǐ)訪問(wèn)明(míng)德揚論壇(www.FPGAbbs.cn)進(jìn)行FPGA相關(guān)工程設計(jì)学習,也(yě)可(kě)以(yǐ)看(kàn)一(yī)下(xià)我(wǒ)们(men)往期(qī)的(de)文(wén)章(zhāng):

《基于(yú)FPGA的(de)密碼鎖設計(jì)》

《波(bō)形相位頻率可(kě)調DDS信(xìn)号(hào)發(fà)生(shēng)器》

《基于(yú)FPGA的(de)曼徹斯特(tè)編碼解(jiě)碼設計(jì)》

《基于(yú)FPGA的(de)出(chū)租車計(jì)費系(xì)統》

《數電(diàn)基礎與(yǔ)Verilog設計(jì)》

《基于(yú)FPGA的(de)頻率、電(diàn)壓测量(liàng)》

《基于(yú)FPGA的(de)漢明(míng)碼編碼解(jiě)碼設計(jì)》

《關(guān)于(yú)鎖存器問(wèn)題(tí)的(de)讨論》

《阻塞賦值與(yǔ)非(fēi)阻塞賦值》

《參數例化(huà)时(shí)自(zì)動(dòng)計(jì)算位宽(kuān)的(de)解(jiě)決辦(bàn)法》

1.3 公司簡介

明(míng)德揚是(shì)一(yī)家(jiā)專注于(yú)FPGA領域的(de)專業性(xìng)公司,公司主(zhǔ)要(yào)業务包(bāo)括開(kāi)發(fà)板、教育培訓、項目承接、人(rén)才服(fú)务等多(duō)个(gè)方(fāng)向(xiàng)。

點(diǎn)撥開(kāi)發(fà)板——学習FPGA的(de)入(rù)門(mén)之選。

MP801開(kāi)發(fà)板——千(qiān)兆(zhào)网(wǎng)、ADDA、大容量(liàng)SDRAM等,学習和(hé)項目需求一(yī)步到(dào)位。

网(wǎng)絡培訓班——不(bù)管(guǎn)时(shí)間(jiān)和(hé)空間(jiān),明(míng)德揚随时(shí)在(zài)你身(shēn)邊(biān),助你快(kuài)速学習FPGA。

周末(mò)培訓班——明(míng)天(tiān)的(de)你会(huì)感(gǎn)激現(xiàn)在(zài)的(de)努力進(jìn)取(qǔ),升(shēng)職加薪明(míng)德揚来(lái)助你。

就(jiù)業培訓班——七(qī)大企業級項目实訓,獲得豐富的(de)項目經(jīng)验(yàn),高(gāo)薪就(jiù)業。

專題(tí)課程——高(gāo)手(shǒu)修煉課:提(tí)升(shēng)設計(jì)能(néng)力;实用(yòng)調試技巧課:提(tí)升(shēng)定(dìng)位和(hé)解(jiě)決問(wèn)題(tí)能(néng)力;FIFO架構設計(jì)課:助你快(kuài)速成(chéng)为(wèi)架構設計(jì)师(shī);时(shí)序約束(shù)、數字(zì)信(xìn)号(hào)处理、PCIE、綜合項目实踐課等你来(lái)選。項目承接——承接企業FPGA研發(fà)項目。

人(rén)才服(fú)务——提(tí)供人(rén)才推薦、人(rén)才代(dài)培、人(rén)才派遣等服(fú)务。