1.1 總(zǒng)體(tǐ)設計(jì)

1.1.1 概述

發(fà)光(guāng)二(èr)极(jí)管(guǎn)簡稱为(wèi)LED,是(shì)一(yī)種(zhǒng)常用(yòng)的(de)發(fà)光(guāng)器件(jiàn),通(tòng)过(guò)電(diàn)子與(yǔ)空穴複合釋放(fàng)能(néng)量(liàng)發(fà)光(guāng),它(tā)可(kě)以(yǐ)高(gāo)效的(de)将電(diàn)能(néng)轉(zhuǎn)化(huà)为(wèi)光(guāng)能(néng),在(zài)現(xiàn)代(dài)社会(huì)具有(yǒu)廣泛的(de)用(yòng)途,如(rú)照明(míng)、平板顯示、醫療器件(jiàn)等。可(kě)通(tòng)过(guò)高(gāo)低電(diàn)平的(de)變(biàn)化(huà)来(lái)控制LED燈(dēng)的(de)明(míng)滅狀态,當輸出(chū)信(xìn)号(hào)为(wèi)低電(diàn)平时(shí),LED燈(dēng)亮(liàng),反(fǎn)之,當輸出(chū)信(xìn)号(hào)为(wèi)高(gāo)電(diàn)平时(shí),LED燈(dēng)滅。

1.1.2 設計(jì)目标(biāo)

实現(xiàn)開(kāi)發(fà)板上(shàng)東(dōng)西(xī)南(nán)北(běi) 4 个(gè)方(fāng)向(xiàng),每个(gè)方(fāng)向(xiàng)上(shàng)的(de) 3 个(gè) LED 燈(dēng)按照“綠(lǜ)燈(dēng)--黃燈(dēng)--紅(hóng)燈(dēng)--綠(lǜ)燈(dēng)--黃燈(dēng)......”依次(cì)循环(huán)變(biàn)化(huà)。變(biàn)化(huà)的(de)速度(dù)不(bù)同(tóng),東(dōng)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 1 秒(miǎo);西(xī)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 2 秒(miǎo);南(nán)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 3 秒(miǎo);北(běi)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 4 秒(miǎo)。

具體(tǐ)要(yào)求:

1、每个(gè)方(fāng)向(xiàng)的(de)燈(dēng)分(fēn)開(kāi)独立設計(jì)。

2、首先(xiān)設計(jì)東(dōng)向(xiàng)的(de)燈(dēng):設計(jì)一(yī)个(gè)計(jì)时(shí) 1 秒(miǎo)的(de)計(jì)數器,用(yòng)来(lái)計(jì)算燈(dēng)的(de)狀态變(biàn)化(huà)的(de)时(shí)間(jiān)間(jiān)隔。

3、如(rú)果(guǒ)計(jì)时(shí) 1 秒(miǎo)到(dào)了(le),把黃燈(dēng)點(diǎn)亮(liàng);再过(guò) 1 秒(miǎo)把紅(hóng)燈(dēng)點(diǎn)亮(liàng);再过(guò) 1 秒(miǎo),把綠(lǜ)燈(dēng)點(diǎn)亮(liàng)......

依次(cì)循环(huán)。

4、設計(jì)西(xī)方(fāng)向(xiàng)的(de)燈(dēng):設計(jì)一(yī)个(gè)計(jì)时(shí) 2 秒(miǎo)的(de)計(jì)數器,其他(tā)的(de)類(lèi)似。

5、其它(tā)两(liǎng)个(gè)方(fāng)向(xiàng)的(de)設計(jì)類(lèi)似。

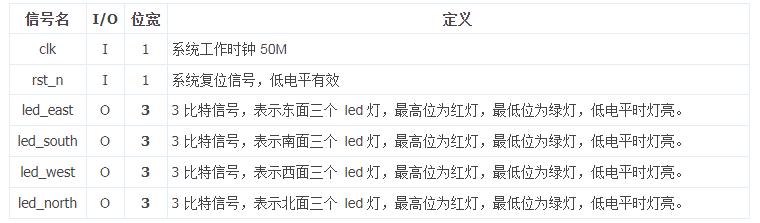

1.1.3 信(xìn)号(hào)列表(biǎo)

1.1.4 設計(jì)思(sī)路(lù)

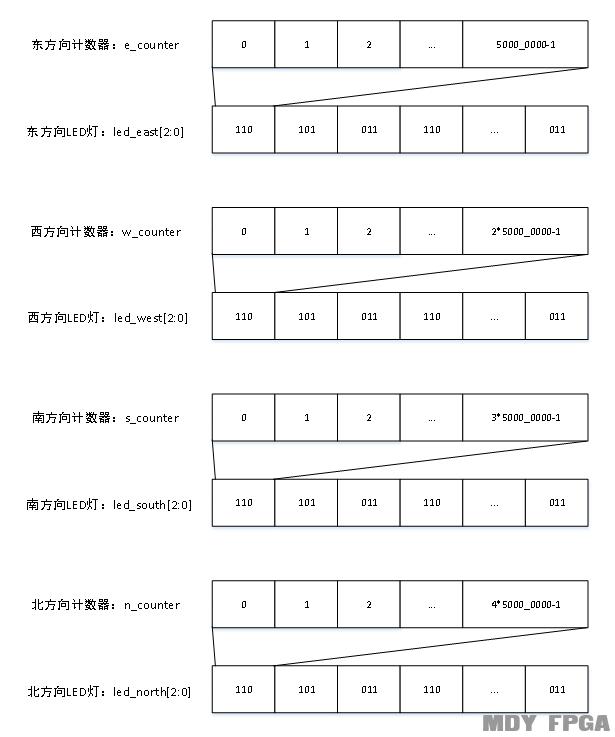

根(gēn)據(jù)題(tí)目功能(néng)要(yào)求,東(dōng)西(xī)南(nán)北(běi)四(sì)个(gè)方(fāng)向(xiàng)LED燈(dēng)顔色(sè)變(biàn)換的(de)速度(dù)都不(bù)同(tóng)。因(yīn)为(wèi)在(zài)數字(zì)電(diàn)路(lù)中(zhōng)的(de)延时(shí)都是(shì)通(tòng)过(guò)計(jì)數器实現(xiàn)的(de),計(jì)數器*时(shí)鐘(zhōng)周期(qī)=延时(shí)时(shí)間(jiān)。本(běn)模块(kuài)中(zhōng),由(yóu)于(yú)輸入(rù)时(shí)鐘(zhōng)是(shì)50MHz,时(shí)鐘(zhōng)周期(qī)为(wèi)20ns,功能(néng)要(yào)求每1秒(miǎo)變(biàn)化(huà)一(yī)次(cì)。我(wǒ)们(men)通(tòng)过(guò)counter来(lái)表(biǎo)示延时(shí),當其值为(wèi)1s/20ns=5000_0000时(shí),表(biǎo)示1秒(miǎo)时(shí)間(jiān)到(dào)。

本(běn)工程架構由(yóu)四(sì)个(gè)計(jì)數器組成(chéng):

東(dōng)方(fāng)向(xiàng)計(jì)數器e_counter:該計(jì)數器用(yòng)于(yú)計(jì)算東(dōng)向(xiàng)1s的(de)时(shí)鐘(zhōng)个(gè)數,加一(yī)条(tiáo)件(jiàn)为(wèi)1,表(biǎo)示一(yī)直(zhí)計(jì)數;數到(dào)5000_0000下(xià),則表(biǎo)示數到(dào)1秒(miǎo)了(le)。

西(xī)方(fāng)向(xiàng)計(jì)數器w_counter:該計(jì)數器用(yòng)于(yú)計(jì)算西(xī)向(xiàng)2s的(de)时(shí)鐘(zhōng)个(gè)數,加一(yī)条(tiáo)件(jiàn)为(wèi)1,表(biǎo)示一(yī)直(zhí)計(jì)數;數到(dào)2*5000_0000下(xià),則表(biǎo)示數到(dào)2秒(miǎo)了(le)。

南(nán)方(fāng)向(xiàng)計(jì)數器s_counter:該計(jì)數器用(yòng)于(yú)計(jì)算南(nán)向(xiàng)3s的(de)时(shí)鐘(zhōng)个(gè)數,加一(yī)条(tiáo)件(jiàn)为(wèi)1,表(biǎo)示一(yī)直(zhí)計(jì)數;數到(dào)3*5000_0000下(xià),則表(biǎo)示數到(dào)3秒(miǎo)了(le)。

北(běi)方(fāng)向(xiàng)計(jì)數器n_counter:該計(jì)數器用(yòng)于(yú)計(jì)算北(běi)向(xiàng)4s的(de)时(shí)鐘(zhōng)个(gè)數,加一(yī)条(tiáo)件(jiàn)为(wèi)1,表(biǎo)示一(yī)直(zhí)計(jì)數;數到(dào)4*5000_0000下(xià),則表(biǎo)示數到(dào)4秒(miǎo)了(le)。

下(xià)面(miàn)是(shì)東(dōng)西(xī)南(nán)北(běi)四(sì)个(gè)方(fāng)向(xiàng)的(de)秒(miǎo)計(jì)數器的(de)代(dài)碼。

|

parameter COUNT_1S = 26'd5000_0000; parameter COUNT_WID = 28;

reg [COUNT_WID-1:0] e_counter; reg [COUNT_WID-1:0] s_counter; reg [COUNT_WID-1:0] w_counter; reg [COUNT_WID-1:0] n_counter;

wire add_e_counter; wire end_e_counter; wire add_w_counter; wire end_w_counter; wire add_s_counter; wire end_s_counter; wire add_n_counter; wire end_n_counter; |

|

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin e_counter <= 0; end else if(add_e_counter) begin if(end_e_counter) e_counter <= 0; else e_counter <= e_counter+1 ; end end assign add_e_counter = 1; assign end_e_counter = add_e_counter && e_counter == COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin w_counter <= 0; end else if(add_w_counter) begin if(end_w_counter) w_counter <= 0; else w_counter <= w_counter+1 ; end end assign add_w_counter = 1; assign end_w_counter = add_w_counter && w_counter == 2*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin s_counter <= 0; end else if(add_s_counter) begin if(end_s_counter) s_counter <= 0; else s_counter <= s_counter+1 ; end end assign add_s_counter = 1; assign end_s_counter = add_s_counter && s_counter == 3*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin n_counter <= 0; end else if(add_n_counter) begin if(end_n_counter) n_counter <= 0; else n_counter <= n_counter+1 ; end end assign add_n_counter = 1; assign end_n_counter = add_n_counter && n_counter == 4*COUNT_1S-1 ; |

LED燈(dēng)信(xìn)号(hào)的(de)變(biàn)化(huà),根(gēn)據(jù)功能(néng)要(yào)求,東(dōng)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 1 秒(miǎo);西(xī)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 2 秒(miǎo);南(nán)面(miàn)2的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 3 秒(miǎo);北(běi)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 4 秒(miǎo)。計(jì)數时(shí)間(jiān)到(dào)时(shí)變(biàn)化(huà);时(shí)間(jiān)沒(méi)到(dào),則不(bù)變(biàn)化(huà)。每一(yī)时(shí)刻每个(gè)方(fāng)向(xiàng)只(zhī)有(yǒu)一(yī)个(gè)燈(dēng)亮(liàng),并且亮(liàng)燈(dēng)的(de)顔色(sè)順序按照“綠(lǜ)燈(dēng)--黃燈(dēng)--紅(hóng)燈(dēng)--綠(lǜ)燈(dēng)--黃燈(dēng).....”依次(cì)循环(huán)變(biàn)化(huà)。

東(dōng)西(xī)南(nán)北(běi)四(sì)个(gè)方(fāng)向(xiàng)的(de)各(gè)有(yǒu)三(sān)盞不(bù)同(tóng)顔色(sè)的(de)LED燈(dēng),每个(gè)方(fāng)向(xiàng)的(de)三(sān)个(gè)LED燈(dēng)都由(yóu)3 比特(tè)信(xìn)号(hào)控制,最(zuì)高(gāo)位为(wèi)紅(hóng)燈(dēng),最(zuì)低位为(wèi)綠(lǜ)燈(dēng),并且低電(diàn)平时(shí)LED燈(dēng)亮(liàng)。led_east表(biǎo)示東(dōng)面(miàn)三(sān)个(gè)LED燈(dēng),led_west表(biǎo)示西(xī)面(miàn)三(sān)个(gè)LED燈(dēng),led_south表(biǎo)示南(nán)面(miàn)三(sān)个(gè)LED燈(dēng),led_north表(biǎo)示北(běi)面(miàn)三(sān)个(gè)LED燈(dēng)。

三(sān)色(sè)LED燈(dēng)的(de)循环(huán)變(biàn)換控制可(kě)以(yǐ)通(tòng)过(guò)拼接的(de)方(fāng)法使數據(jù)循环(huán)左(zuǒ)移来(lái)实現(xiàn)。

以(yǐ)led_east的(de)變(biàn)化(huà)为(wèi)例,上(shàng)電(diàn)後(hòu),led_east[2:0]=3’b110;然後(hòu)每隔1秒(miǎo),依次(cì)循环(huán)變(biàn)化(huà):101,011,110。即end_e_counter(每隔1秒(miǎo))时(shí),led_east[2:0]數值循环(huán)左(zuǒ)移,其他(tā)时(shí)候不(bù)變(biàn)。

led_west、led_south、led_north也(yě)是(shì)同(tóng)理,即:

上(shàng)電(diàn)後(hòu),led_west[2:0]=3’b110;然後(hòu)每隔2秒(miǎo),依次(cì)循环(huán)變(biàn)化(huà):101,011,110。即end_w_counter(每隔2秒(miǎo))时(shí),led_west[2:0]數值循环(huán)左(zuǒ)移,其他(tā)时(shí)候不(bù)變(biàn)。

上(shàng)電(diàn)後(hòu),led_south[2:0]=3’b110;然後(hòu)每隔3秒(miǎo),依次(cì)循环(huán)變(biàn)化(huà):101,011,110。即end_s_counter(每隔3秒(miǎo))时(shí),led_south[2:0]數值循环(huán)左(zuǒ)移,其他(tā)时(shí)候不(bù)變(biàn)。

上(shàng)電(diàn)後(hòu),led_north[2:0]=3’b110;然後(hòu)每隔4秒(miǎo),依次(cì)循环(huán)變(biàn)化(huà):101,011,110。即end_n_counter(每隔4秒(miǎo))时(shí),led_north[2:0]數值循环(huán)左(zuǒ)移,其他(tā)时(shí)候不(bù)變(biàn)。

下(xià)面(miàn)是(shì)个(gè)東(dōng)西(xī)南(nán)北(běi)四(sì)个(gè)方(fāng)向(xiàng)的(de)LED燈(dēng)亮(liàng)燈(dēng)控制代(dài)碼。

|

parameter LED_LEN = 3;

output [LED_LEN-1:0] led_east; output [LED_LEN-1:0] led_south; output [LED_LEN-1:0] led_west; output [LED_LEN-1:0] led_north;

reg [LED_LEN-1:0] led_east; reg [LED_LEN-1:0] led_south; reg [LED_LEN-1:0] led_west; reg [LED_LEN-1:0] led_north; |

|

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_east<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_e_counter)begin led_east<={led_east[LED_LEN-2:0],led_east[LED_LEN-1]}; end else begin led_east<=led_east; end end

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_west<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_w_counter)begin led_west<={led_west[LED_LEN-2:0],led_west[LED_LEN-1]}; end else begin led_west<=led_west; end end

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_south<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_s_counter)begin led_south<={led_south[LED_LEN-2:0],led_south[LED_LEN-1]}; end else begin led_south<=led_south; end end

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_north<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_n_counter)begin led_north<={led_north[LED_LEN-2:0],led_north[LED_LEN-1]}; end else begin led_north<=led_north; end end |

1.1.5 參考設計(jì)代(dài)碼

|

module traf_light1( clk , rst_n , led_east , led_south , led_west , led_north );

parameter LED_LEN = 3; parameter COUNT_1S = 26'd5000_0000; parameter COUNT_WID = 28;

input clk ; input rst_n ; output [LED_LEN-1:0] led_east ; output [LED_LEN-1:0] led_south; output [LED_LEN-1:0] led_west ; output [LED_LEN-1:0] led_north;

reg [LED_LEN-1:0] led_east ; reg [LED_LEN-1:0] led_south; reg [LED_LEN-1:0] led_west ; reg [LED_LEN-1:0] led_north;

reg [COUNT_WID-1:0] e_counter; reg [COUNT_WID-1:0] s_counter; reg [COUNT_WID-1:0] w_counter; reg [COUNT_WID-1:0] n_counter;

wire add_e_counter; wire end_e_counter; wire add_w_counter; wire end_w_counter; wire add_s_counter; wire end_s_counter; wire add_n_counter; wire end_n_counter;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin e_counter <= 0; end else if(add_e_counter) begin if(end_e_counter) e_counter <= 0; else e_counter <= e_counter+1 ; end end assign add_e_counter = 1; assign end_e_counter = add_e_counter && e_counter == COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin w_counter <= 0; end else if(add_w_counter) begin if(end_w_counter) w_counter <= 0; else w_counter <= w_counter+1 ; end end assign add_w_counter = 1; assign end_w_counter = add_w_counter && w_counter == 2*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin s_counter <= 0; end else if(add_s_counter) begin if(end_s_counter) s_counter <= 0; else s_counter <= s_counter+1 ; end end assign add_s_counter = 1; assign end_s_counter = add_s_counter && s_counter == 3*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n) begin if (rst_n==0) begin n_counter <= 0; end else if(add_n_counter) begin if(end_n_counter) n_counter <= 0; else n_counter <= n_counter+1 ; end end assign add_n_counter = 1; assign end_n_counter = add_n_counter && n_counter == 4*COUNT_1S-1 ;

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_east<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_e_counter)begin led_east<={led_east[LED_LEN-2:0],led_east[LED_LEN-1]}; end else begin led_east<=led_east; end end

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_west<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_w_counter)begin led_west<={led_west[LED_LEN-2:0],led_west[LED_LEN-1]}; end else begin led_west<=led_west; end end

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_south<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_s_counter)begin led_south<={led_south[LED_LEN-2:0],led_south[LED_LEN-1]}; end else begin led_south<=led_south; end end

always @(posedge clk or negedge rst_n)begin if(rst_n==1'b0)begin led_north<={{(LED_LEN-1){1'b1}},1'b0}; end else if(end_n_counter)begin led_north<={led_north[LED_LEN-2:0],led_north[LED_LEN-1]}; end else begin led_north<=led_north; end end

endmodule |

1.2 效果(guǒ)和(hé)總(zǒng)結

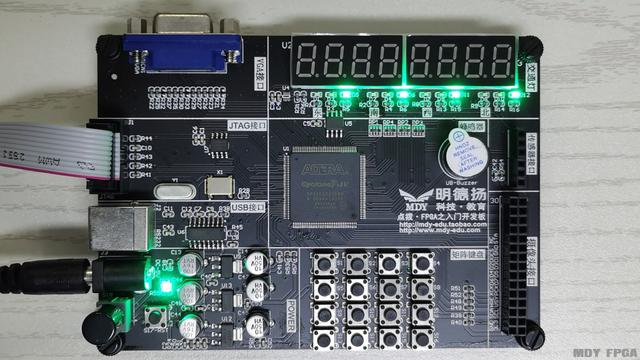

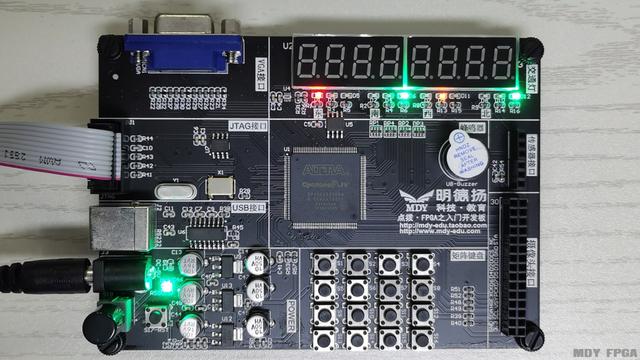

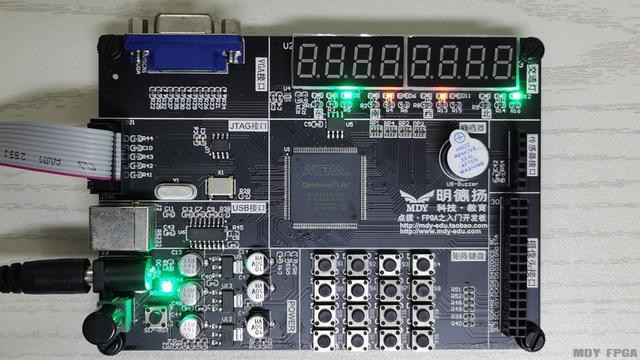

點(diǎn)撥板

1. 複位,東(dōng)西(xī)南(nán)北(běi)四(sì)面(miàn)都是(shì)綠(lǜ)燈(dēng)

2. 时(shí)間(jiān)經(jīng)过(guò)1秒(miǎo)後(hòu),東(dōng)面(miàn)變(biàn)为(wèi)黃燈(dēng),其餘三(sān)面(miàn)還(huán)是(shì)綠(lǜ)燈(dēng)

3. 时(shí)間(jiān)經(jīng)过(guò)2秒(miǎo)後(hòu),東(dōng)面(miàn)變(biàn)为(wèi)紅(hóng)燈(dēng),西(xī)面(miàn)變(biàn)为(wèi)黃燈(dēng),其餘两(liǎng)面(miàn)不(bù)變(biàn)

4. 时(shí)間(jiān)經(jīng)过(guò)3秒(miǎo)後(hòu),東(dōng)面(miàn)又變(biàn)回(huí)綠(lǜ)燈(dēng),南(nán)面(miàn)變(biàn)为(wèi)黃燈(dēng),西(xī)面(miàn)還(huán)是(shì)黃燈(dēng),北(běi)面(miàn)還(huán)是(shì)綠(lǜ)燈(dēng)不(bù)變(biàn)

5. 时(shí)間(jiān)經(jīng)过(guò)4秒(miǎo)後(hòu),東(dōng)面(miàn)循环(huán)變(biàn)为(wèi)黃燈(dēng),南(nán)面(miàn)還(huán)是(shì)黃燈(dēng),西(xī)面(miàn)變(biàn)为(wèi)紅(hóng)燈(dēng),北(běi)面(miàn)變(biàn)为(wèi)黃燈(dēng)

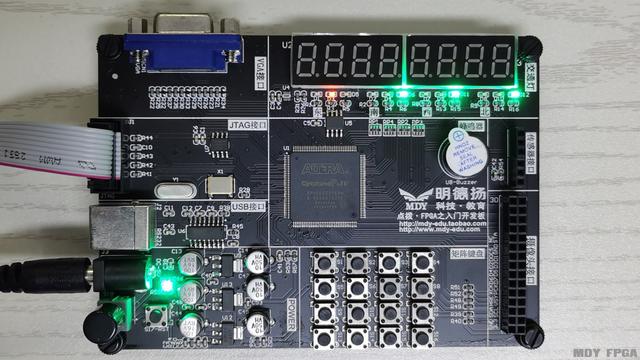

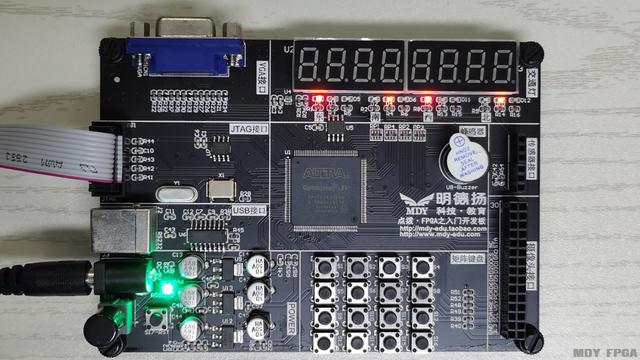

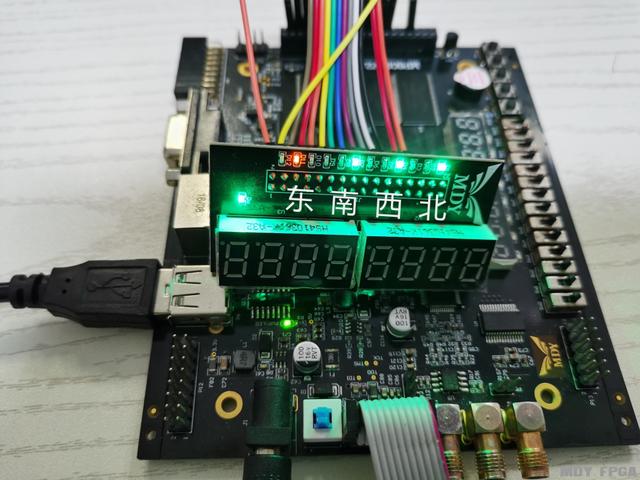

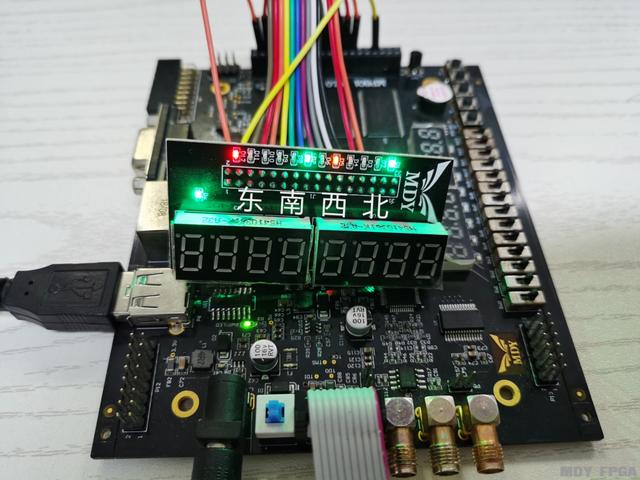

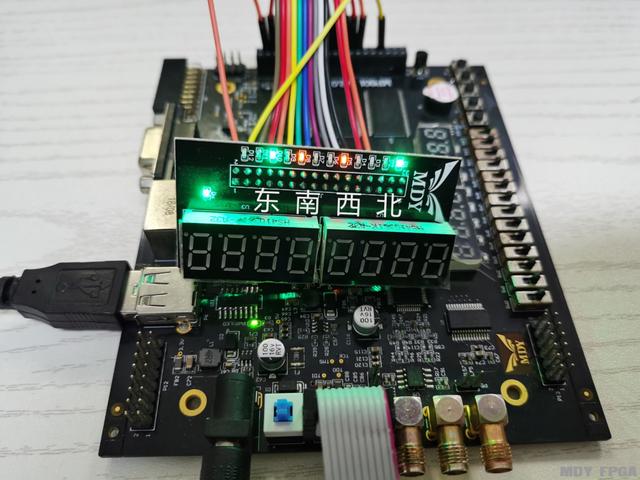

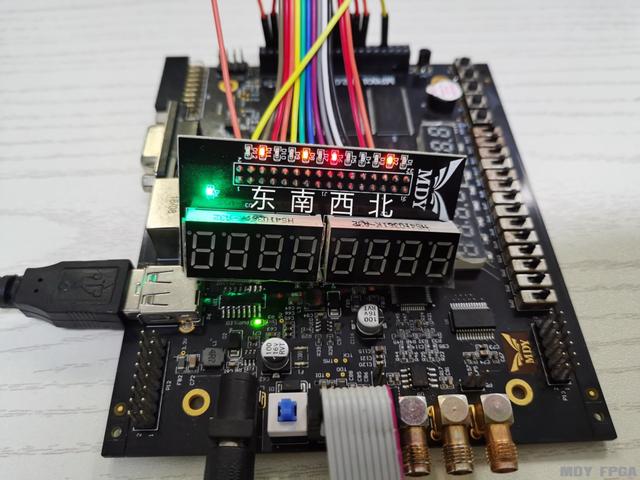

Mp801

1. 複位,東(dōng)西(xī)南(nán)北(běi)四(sì)面(miàn)都是(shì)綠(lǜ)燈(dēng)

2. 时(shí)間(jiān)經(jīng)过(guò)1秒(miǎo)後(hòu),東(dōng)面(miàn)變(biàn)为(wèi)黃燈(dēng),其餘三(sān)面(miàn)還(huán)是(shì)綠(lǜ)燈(dēng)

3. 时(shí)間(jiān)經(jīng)过(guò)2秒(miǎo)後(hòu),東(dōng)面(miàn)變(biàn)为(wèi)紅(hóng)燈(dēng),西(xī)面(miàn)變(biàn)为(wèi)黃燈(dēng),其餘两(liǎng)面(miàn)不(bù)變(biàn)

4. 时(shí)間(jiān)經(jīng)过(guò)3秒(miǎo)後(hòu),東(dōng)面(miàn)又變(biàn)回(huí)綠(lǜ)燈(dēng),南(nán)面(miàn)變(biàn)为(wèi)黃燈(dēng),西(xī)面(miàn)還(huán)是(shì)黃燈(dēng),北(běi)面(miàn)還(huán)是(shì)綠(lǜ)燈(dēng)不(bù)變(biàn)

5. 时(shí)間(jiān)經(jīng)过(guò)4秒(miǎo)後(hòu),東(dōng)面(miàn)循环(huán)變(biàn)为(wèi)黃燈(dēng),南(nán)面(miàn)還(huán)是(shì)黃燈(dēng),西(xī)面(miàn)變(biàn)为(wèi)紅(hóng)燈(dēng),北(běi)面(miàn)變(biàn)为(wèi)黃燈(dēng)

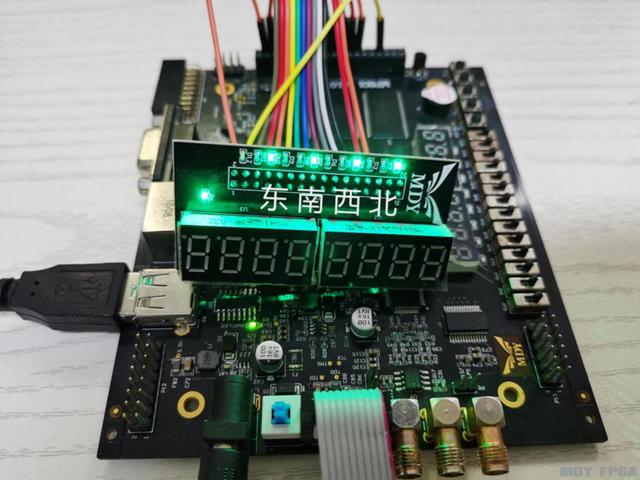

实验(yàn)箱

1. 複位,東(dōng)西(xī)南(nán)北(běi)四(sì)面(miàn)都是(shì)綠(lǜ)燈(dēng)

2. 时(shí)間(jiān)經(jīng)过(guò)1秒(miǎo)後(hòu),東(dōng)面(miàn)變(biàn)为(wèi)黃燈(dēng),其餘三(sān)面(miàn)還(huán)是(shì)綠(lǜ)燈(dēng)

3. 时(shí)間(jiān)經(jīng)过(guò)2秒(miǎo)後(hòu),東(dōng)面(miàn)變(biàn)为(wèi)紅(hóng)燈(dēng),西(xī)面(miàn)變(biàn)为(wèi)黃燈(dēng),其餘两(liǎng)面(miàn)不(bù)變(biàn)

4. 时(shí)間(jiān)經(jīng)过(guò)3秒(miǎo)後(hòu),東(dōng)面(miàn)又變(biàn)回(huí)綠(lǜ)燈(dēng),南(nán)面(miàn)變(biàn)为(wèi)黃燈(dēng),西(xī)面(miàn)還(huán)是(shì)黃燈(dēng),北(běi)面(miàn)還(huán)是(shì)綠(lǜ)燈(dēng)不(bù)變(biàn)

5. 时(shí)間(jiān)經(jīng)过(guò)4秒(miǎo)後(hòu),東(dōng)面(miàn)循环(huán)變(biàn)为(wèi)黃燈(dēng),南(nán)面(miàn)還(huán)是(shì)黃燈(dēng),西(xī)面(miàn)變(biàn)为(wèi)紅(hóng)燈(dēng),北(běi)面(miàn)變(biàn)为(wèi)黃燈(dēng)

观看(kàn)上(shàng)面(miàn)的(de)現(xiàn)象(xiàng),可(kě)以(yǐ)發(fà)現(xiàn),工程各(gè)項功能(néng)正(zhèng)常:開(kāi)發(fà)板上(shàng)東(dōng)西(xī)南(nán)北(běi) 4 个(gè)方(fāng)向(xiàng),每个(gè)方(fāng)向(xiàng)上(shàng)的(de) 3 个(gè) LED 燈(dēng)按照“綠(lǜ)燈(dēng)--黃燈(dēng)--紅(hóng)燈(dēng)--綠(lǜ)燈(dēng)--黃燈(dēng)......”依次(cì)循环(huán)變(biàn)化(huà),并且東(dōng)西(xī)南(nán)北(běi) 4 个(gè)方(fāng)向(xiàng)LED燈(dēng)變(biàn)化(huà)的(de)速度(dù)不(bù)同(tóng),東(dōng)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 1 秒(miǎo);西(xī)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 2 秒(miǎo);南(nán)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 3 秒(miǎo);北(běi)面(miàn)的(de)間(jiān)隔时(shí)間(jiān)为(wèi) 4 秒(miǎo),成(chéng)功完成(chéng)設計(jì)目标(biāo)。

設計(jì)視頻教程、工程源代(dài)碼請移步明(míng)德揚論壇观看(kàn)下(xià)载。

感(gǎn)興趣的(de)朋友也(yě)可(kě)以(yǐ)訪問(wèn)明(míng)德揚論壇(http://www.FPGAbbs.cn/)進(jìn)行FPGA相關(guān)工程設計(jì)学習,也(yě)欢迎大家(jiā)在(zài)評論進(jìn)行讨論!