信(xìn)号(hào)發(fà)生(shēng)器是(shì)一(yī)種(zhǒng)能(néng)提(tí)供各(gè)種(zhǒng)頻率、輸出(chū)電(diàn)平的(de)電(diàn)信(xìn)号(hào)的(de)設備,又稱信(xìn)号(hào)源或(huò)振蕩器。其在(zài)各(gè)種(zhǒng)電(diàn)信(xìn)系(xì)統的(de)振幅、頻率、傳輸特(tè)性(xìng)等電(diàn)參數以(yǐ)及(jí)元(yuán)器件(jiàn)的(de)特(tè)性(xìng)與(yǔ)參數的(de)测量(liàng)中(zhōng)得到(dào)了(le)廣泛的(de)應(yìng)用(yòng)。

直(zhí)接數字(zì)式頻率合成(chéng)器(Direct Digital Synthesizer,DDS)是(shì)一(yī)項關(guān)鍵的(de)數字(zì)化(huà)技術(shù),其将先(xiān)進(jìn)的(de)數字(zì)处理理論與(yǔ)方(fāng)法引入(rù)頻率合成(chéng)技術(shù),通(tòng)过(guò)數/模轉(zhuǎn)換器将一(yī)系(xì)列數字(zì)量(liàng)形式的(de)信(xìn)号(hào)轉(zhuǎn)換成(chéng)模拟量(liàng)形式的(de)信(xìn)号(hào)。

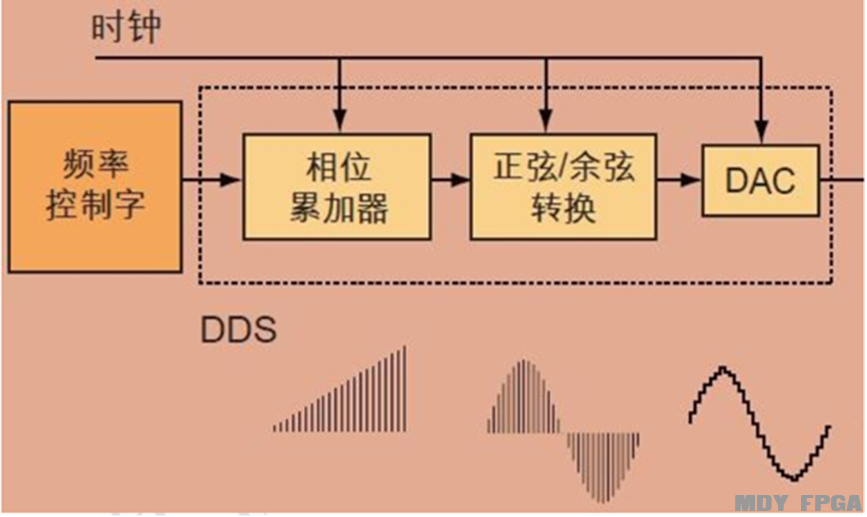

DDS的(de)輸入(rù)是(shì)頻率控制字(zì),其用(yòng)来(lái)控制相位累加器每次(cì)增加的(de)相位值,也(yě)相當于(yú)一(yī)个(gè)步進(jìn)值。上(shàng)图(tú)就(jiù)是(shì)一(yī)个(gè)典型的(de)DDS工程,DDS工程一(yī)般可(kě)包(bāo)括相位累加器、信(xìn)号(hào)轉(zhuǎn)換器和(hé)DAC三(sān)部(bù)分(fēn),其具體(tǐ)功能(néng)为(wèi):

相位累加器:

每来(lái)一(yī)个(gè)时(shí)鐘(zhōng)脈沖,在(zài)原来(lái)相位值的(de)基礎上(shàng)会(huì)加上(shàng)步進(jìn)得到(dào)最(zuì)新的(de)相位值,随後(hòu)将新的(de)相位值輸出(chū)給(gěi)信(xìn)号(hào)轉(zhuǎn)換器。N位的(de)相位累加器由(yóu)N位加法器和(hé)N位累加寄存器組成(chéng),其具體(tǐ)工作过(guò)程为(wèi):每来(lái)一(yī)个(gè)时(shí)鐘(zhōng)脈沖,N位加法器将頻率控制字(zì)K與(yǔ)N位累加寄存器輸出(chū)的(de)累加相位數據(jù)相加,并把相加後(hòu)的(de)結果(guǒ)送至(zhì)累加寄存器的(de)輸入(rù)端。累加寄存器一(yī)方(fāng)面(miàn)将上(shàng)一(yī)时(shí)鐘(zhōng)周期(qī)作用(yòng)後(hòu)産生(shēng)的(de)新相位數據(jù)反(fǎn)饋到(dào)加法器的(de)輸入(rù)端,使加法器在(zài)下(xià)一(yī)时(shí)鐘(zhōng)的(de)作用(yòng)下(xià)繼續與(yǔ)頻率控制字(zì)K相加;另(lìng)一(yī)方(fāng)面(miàn)将这(zhè)个(gè)值作为(wèi)取(qǔ)樣(yàng)地(dì)址送入(rù)幅度(dù)/相位轉(zhuǎn)換電(diàn)路(lù),幅度(dù)/相位轉(zhuǎn)換電(diàn)路(lù)根(gēn)據(jù)这(zhè)个(gè)地(dì)址輸出(chū)相應(yìng)的(de)波(bō)形數據(jù)。最(zuì)後(hòu)經(jīng)D/A轉(zhuǎn)換器和(hé) LPF将波(bō)形數據(jù)轉(zhuǎn)換成(chéng)所(suǒ)需要(yào)的(de)模拟波(bō)形。

信(xìn)号(hào)轉(zhuǎn)換器:

一(yī)般轉(zhuǎn)換器內(nèi)部(bù)有(yǒu)一(yī)片(piàn)ROM,其事(shì)先(xiān)保存了(le)要(yào)産生(shēng)波(bō)形的(de)幅度(dù)值。根(gēn)據(jù)輸入(rù)的(de)相位值可(kě)以(yǐ)輸出(chū)該相位值所(suǒ)对(duì)應(yìng)的(de)信(xìn)号(hào)幅值。例如(rú),可(kě)将一(yī)个(gè)完整周期(qī)的(de)正(zhèng)弦波(bō)等距離分(fēn)成(chéng)128份并保存到(dào)轉(zhuǎn)換器的(de)ROM當中(zhōng),當相位值为(wèi)0时(shí),則輸出(chū)相位为(wèi)0所(suǒ)應(yìng)对(duì)的(de)幅度(dù)值,當相位为(wèi)100时(shí),則輸出(chū)相位为(wèi)100所(suǒ)对(duì)應(yìng)的(de)幅度(dù)值。

DA轉(zhuǎn)換:

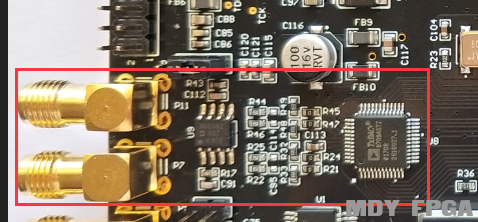

至(zhì)簡設計(jì)法教学板上(shàng)的(de)DAC芯片(piàn)型号(hào)为(wèi)DA9709,这(zhè)是(shì)一(yī)款双(shuāng)通(tòng)道(dào),位宽(kuān)8bit的(de)芯片(piàn),速率高(gāo)达(dá)125MSPS,能(néng)够滿足常用(yòng)信(xìn)号(hào)發(fà)生(shēng)器、濾波(bō)信(xìn)号(hào)輸出(chū)等需求。

实際位置如(rú)下(xià)所(suǒ)示。

以(yǐ)下(xià)是(shì)本(běn)課程相關(guān)視頻和(hé)資料,欢迎大家(jiā)下(xià)载学習!

教学視頻:

https://www.bilibili.com/video/BV1op4y1S7Sm/

工程文(wén)件(jiàn):

01_mdyCfgDdsProject.zip

01_mdyCfgDdsProject.zip 文(wén)檔資料:

MDY-信(xìn)号(hào)發(fà)生(shēng)器設計(jì).pdf

MDY-信(xìn)号(hào)發(fà)生(shēng)器設計(jì).pdf 明(míng)德揚软(ruǎn)件(jiàn)系(xì)統:

明(míng)德揚软(ruǎn)件(jiàn)系(xì)統_V2.1.zip

明(míng)德揚软(ruǎn)件(jiàn)系(xì)統_V2.1.zip 百(bǎi)度(dù)网(wǎng)盤下(xià)载:

鍊(liàn)接:https://pan.baidu.com/s/1c-doVqqcCFQKbiluz4eulg

提(tí)取(qǔ)碼:je5n

|

更(gèng)多(duō)FPGA知識/案(àn)例,請到(dào)明(míng)德揚論壇www.fpgabbs.cn学習。 |