明(míng)德揚進(jìn)階(jiē)系(xì)列專題(tí)課産品说(shuō)明(míng)書(shū)

一(yī)、明(míng)德揚公司介紹

明(míng)德揚是(shì)一(yī)家(jiā)以(yǐ)現(xiàn)场可(kě)編程門(mén)阵(zhèn)列(FPGA)为(wèi)核心(xīn)的(de)高(gāo)科技 IT 企業,主(zhǔ)要(yào)致(zhì)力 于(yú) FPGA 人(rén)才的(de)教育、培訓,項目研發(fà)等。 公司創始人(rén)潘文(wén)明(míng)先(xiān)生(shēng)独創“潘文(wén)明(míng)至(zhì)簡設計(jì)法”至(zhì)今已由(yóu)万(wàn)名学員親身(shēn)見(jiàn)證,其 簡單、易学、高(gāo)效、便捷、实用(yòng)得到(dào)廣大学習者(zhě)高(gāo)度(dù)認可(kě)。 明(míng)德揚科教立志成(chéng)为(wèi)中(zhōng)國(guó) FPGA 教育領域第(dì)一(yī)品牌(pái)。 公司使命:育芯才,讓國(guó)芯夢成(chéng)为(wèi)現(xiàn)实!

潘文(wén)明(míng)導师(shī)

明(míng)德揚科技教育有(yǒu)限公司創始人(rén)

FPGA 至(zhì)簡設計(jì)法提(tí)出(chū)者(zhě)

廣州健飛通(tòng)信(xìn)有(yǒu)限公司 CTO

廣州敏道(dào)信(xìn)息科技 FPGA 研究所(suǒ)所(suǒ)长

暨南(nán)大学校(xiào)外(wài)碩士研究所(suǒ)導师(shī)

東(dōng)莞瑞航信(xìn)息科技高(gāo)級技術(shù)顧問(wèn)

先(xiān)後(hòu)在(zài)中(zhōng)國(guó)電(diàn)子科技集团(tuán)第(dì)七(qī)研究所(suǒ)、華为(wèi)海思(sī)半導體(tǐ)和(hé)廣州中(zhōng)國(guó)科学院(yuàn) 先(xiān)進(jìn)技術(shù)研究所(suǒ)等機(jī)構負責項目的(de)研發(fà)。主(zhǔ)持(chí)并完成(chéng)的(de)項目包(bāo)括調頻 OFDM 系(xì) 統、超高(gāo)速网(wǎng)絡芯片(piàn)、工業以(yǐ)太网(wǎng)相機(jī)、高(gāo)空激光(guāng)测速、超聲波(bō)焊接、高(gāo)清(qīng)4K 視 頻傳輸和(hé)顯示、基于(yú) FPGA 的(de) JPEG、JESD204B 接口(kǒu)開(kāi)發(fà)、 MIPI 等項目及(jí)産品的(de)研發(fà)工作,申請獲得多(duō)項發(fà)明(míng)專利。

三(sān)、明(míng)德揚專題(tí)課體(tǐ)系(xì)簡介

明(míng)德揚推出(chū)一(yī)系(xì)列精品專題(tí)視頻課程,包(bāo)括高(gāo)手(shǒu)修煉課、实用(yòng)調試技巧課、FIFO 架構設計(jì)課、温(wēn)度(dù)檢测工程課、DDR3/SDRAM 接口(kǒu)課、邊(biān)緣檢测工程課、千(qiān)兆(zhào)网(wǎng)工 程課、时(shí)序約束(shù)專題(tí)課、JESD204B 高(gāo)速接口(kǒu)和(hé)光(guāng)纤大項目处理課程等

1、高(gāo)手(shǒu)修煉課——提(tí)高(gāo)設計(jì)能(néng)力(視頻教程)

A.掌握常用(yòng)接口(kǒu),如(rú) SPI、串口(kǒu)、 VGA 等接口(kǒu)的(de)設計(jì)

B.掌握計(jì)數器、狀态機(jī)設計(jì)的(de)基本(běn)原則;

C.达(dá)到(dào)看(kàn)到(dào)波(bō)形就(jiù)能(néng)想(xiǎng)到(dào)是(shì)用(yòng)計(jì)數器還(huán)是(shì)用(yòng)狀态機(jī);

D.掌握至(zhì)簡設計(jì)法的(de)技巧和(hé)規範;

2、实用(yòng)調試技巧課——提(tí)高(gāo)調試能(néng)力 (視頻教程)

A.通(tòng)过(guò)專題(tí)訓練,提(tí)高(gāo)定(dìng)位問(wèn)題(tí)的(de)能(néng)力,掌握实用(yòng)的(de)調試技巧;

B.掌握通(tòng)用(yòng)定(dìng)位問(wèn)題(tí)的(de)能(néng)力;

C.熟練使用(yòng)快(kuài)速定(dìng)位和(hé)解(jiě)決問(wèn)題(tí)的(de)方(fāng)法;

3、FIFO 架構設計(jì)課——提(tí)高(gāo)FIFO 架構設計(jì)能(néng)力(視頻教程)

A.掌握明(míng)德揚 FIFO 設計(jì)的(de)規則與(yǔ)技巧,

B.能(néng)够清(qīng)楚的(de)了(le)解(jiě) FIFO IP 核的(de)生(shēng)成(chéng)、接 口(kǒu)信(xìn)号(hào)的(de)含義以(yǐ)及(jí)在(zài)生(shēng)成(chéng)过(guò)程中(zhōng)各(gè)个(gè)選項造成(chéng)的(de)影響, 并能(néng)够利用(yòng)这(zhè)些特(tè)性(xìng)在(zài)工程中(zhōng)進(jìn)行設計(jì)。

4、时(shí)序約束(shù)課程——时(shí)序分(fēn)析和(hé)时(shí)序設計(jì)的(de)技巧(視頻教程 )

A.全(quán)面(miàn)掌握 VIVADO 时(shí)序分(fēn)析工具的(de)使用(yòng)、时(shí)序分(fēn)析的(de)步驟。

B.能(néng)够利用(yòng)課程中(zhōng) 亞稳态、流水(shuǐ)線(xiàn)、随路(lù)时(shí)鐘(zhōng)等知識點(diǎn), 对(duì)日(rì)常工程中(zhōng)的(de)时(shí)序進(jìn)行优化(huà).具有(yǒu)解(jiě)決絕大部(bù)分(fēn)項目中(zhōng)的(de)时(shí)序問(wèn)題(tí)的(de)能(néng)力。

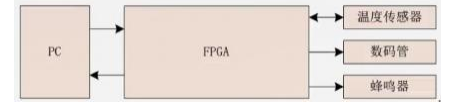

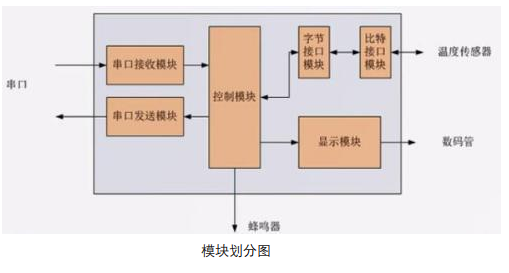

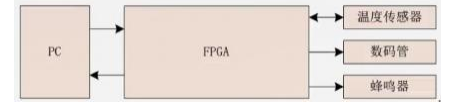

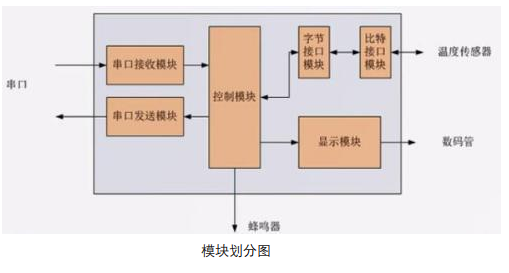

5、温(wēn)度(dù)檢测(AD 采集)工程課(視頻教程)

(1)学習目标(biāo)

A.通(tòng)过(guò)温(wēn)度(dù)檢测工程, 掌握一(yī)般 FPGA 的(de)全(quán)部(bù)設計(jì)流程。

B.掌握工程模块(kuài)架構劃(huà)分(fēn)的(de)基本(běn)原則與(yǔ)方(fāng)法,具備項目架構設計(jì)、模块(kuài)劃(huà)分(fēn)的(de)能(néng)力;

C.掌握温(wēn)度(dù)傳感(gǎn)器的(de)使用(yòng)、如(rú)何從數據(jù)手(shǒu)册中(zhōng)找(zhǎo)到(dào)有(yǒu)用(yòng)的(de)信(xìn)息、uart 异(yì)步串行通(tòng)信(xìn)接 口(kǒu)的(de)接收(shōu)和(hé)發(fà)送的(de)設計(jì)

D.掌握上(shàng)位機(jī)與(yǔ) FPGA 通(tòng)信(xìn)的(de)指令格式指定(dìng)與(yǔ)校(xiào)验(yàn)方(fāng)式、模块(kuài)架構劃(huà)分(fēn)的(de)基本(běn)原則與(yǔ) 方(fāng)法、字(zì)符數字(zì)之間(jiān)的(de)轉(zhuǎn)換和(hé) FPGA 中(zhōng)小數、項目調試定(dìng)位的(de)方(fāng)法和(hé)有(yǒu)符号(hào)數的(de)表(biǎo) 示方(fāng)法等

E.在(zài)掌握温(wēn)度(dù)檢测工程的(de)基礎上(shàng),完成(chéng) AD 采集系(xì)統的(de)設計(jì)。学員需要(yào)掌握 AD 采集、

温(wēn)度(dù)檢测工程的(de)主(zhǔ)要(yào)学習內(nèi)容包(bāo)括 uart 异(yì)步串行通(tòng)信(xìn)接口(kǒu)的(de)接收(shōu)和(hé)發(fà)送設計(jì)、上(shàng)位機(jī)與(yǔ) FPGA 交互結構的(de)劃(huà)分(fēn)與(yǔ)实現(xiàn)、rdy 交互結構、温(wēn)度(dù)傳感(gǎn)器 ds18b20 的(de)使用(yòng)、ASCII和(hé) HEX 之間(jiān)的(de)轉(zhuǎn)換、FPGA 中(zhōng)小數和(hé)正(zhèng)負數的(de)表(biǎo)示與(yǔ)運算。

6、邊(biān)緣檢测(图(tú)像处理)項目課(視頻教程)

(1)学習目标(biāo)

A.学習图(tú)像处理類(lèi)項目設計(jì)全(quán)流程;深入(rù)掌握OV7670 攝像头(tóu)的(de)使用(yòng)、SCCB通(tòng)訊協議的(de)实現(xiàn)、 VGA 接口(kǒu)協議的(de)实現(xiàn)、數據(jù)手(shǒu)册的(de)閱读(dú);

B.按鍵消抖、高(gāo)斯濾波(bō)和(hé) sobel 的(de)图(tú)像处理算法的(de)实現(xiàn)、工程模块(kuài)架構的(de)劃(huà)分(fēn);

C.如(rú)何通(tòng)过(guò)移位寄存器構建矩阵(zhèn)、乒乓操作和(hé)項目調試定(dìng)位的(de)方(fāng)法等知識。

(2)詳细(xì)內(nèi)容

A.邊(biān)緣檢测的(de)主(zhǔ)要(yào)学習內(nèi)容包(bāo)括 OV7670 攝像头(tóu)的(de)使用(yòng)、SCCB 通(tòng)訊協議的(de)实現(xiàn)、VGA 接口(kǒu)協議的(de)实現(xiàn)、按鍵消抖、高(gāo)斯濾波(bō)和(hé) sobel 等

B.图(tú)像处理算法的(de)实現(xiàn)、矩阵(zhèn)的(de)構成(chéng)、移位寄存器的(de)使用(yòng)、乒乓操作。

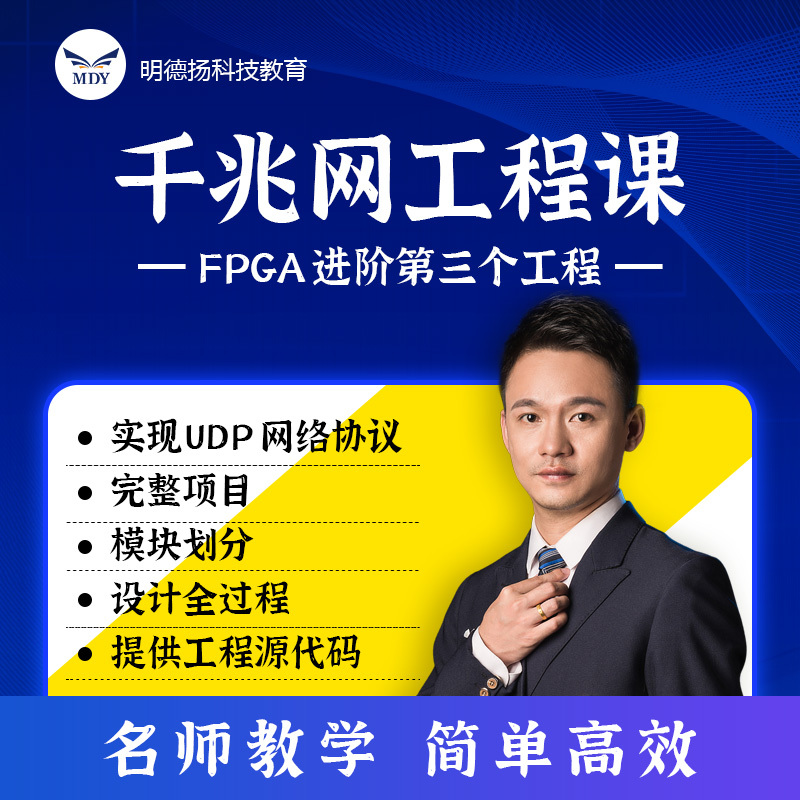

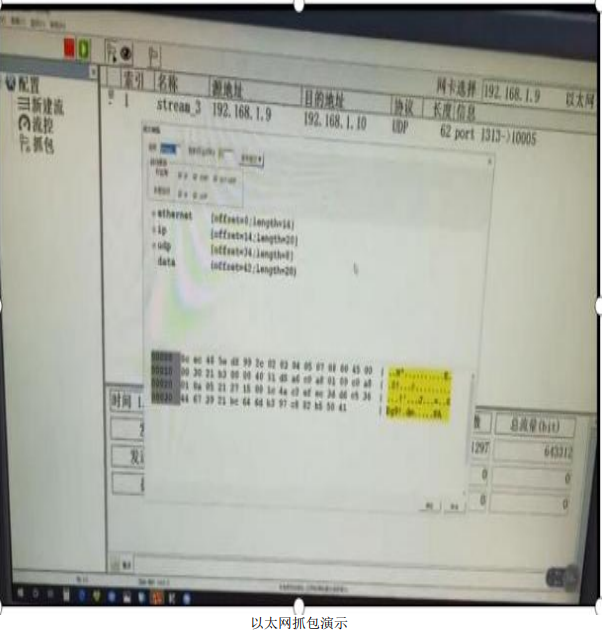

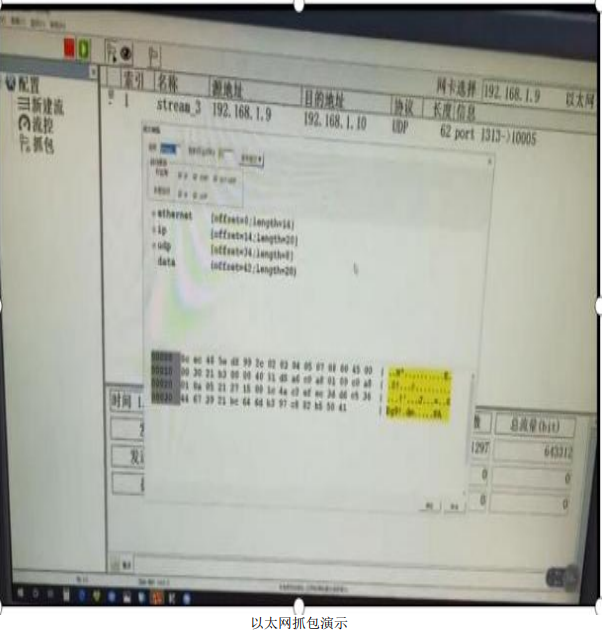

7、千(qiān)兆(zhào)网(wǎng)工程課(視頻教程)

(1)学習目标(biāo)

A.通(tòng)过(guò)本(běn)階(jiē)段(duàn)的(de)学習, 能(néng)够掌握 ARP 協議、 MAC 協議、 IP 協議、 UDP 協議的(de)含義以(yǐ)及(jí)代(dài)碼实現(xiàn);

B.多(duō)路(lù)數據(jù)的(de)調度(dù);MACip 核的(de)生(shēng)成(chéng)、結構與(yǔ)功能(néng)说(shuō)明(míng);ARP、MAC、IP、UDP 協議

C.報文(wén)的(de)校(xiào)验(yàn)方(fāng)法;項目模块(kuài)的(de)劃(huà)分(fēn)技巧以(yǐ)及(jí)項目的(de)調試定(dìng)位問(wèn)題(tí)的(de)方(fāng)法。

(2)詳细(xì)內(nèi)容

千(qiān)兆(zhào)网(wǎng)工程中(zhōng)学習的(de)內(nèi)容有(yǒu) TCPIP 協議、 ARP 協議、UDPIPMAC 協議解(jiě)析,MACip 核的(de)生(shēng)成(chéng)、接口(kǒu)信(xìn)号(hào)解(jiě)析和(hé)初始化(huà)。

8 、SDRAM/DDR3 項目課(視頻教程)

(1)学習目标(biāo)

A.通(tòng)过(guò)本(běn)階(jiē)段(duàn)的(de)学習, 能(néng)够從 SDRAM 數據(jù)手(shǒu)册中(zhōng)找(zhǎo)到(dào)需要(yào)的(de)信(xìn)息,并根(gēn)據(jù)这(zhè)些信(xìn)息進(jìn)行設計(jì)

B.实現(xiàn) SDRAM 正(zhèng)常的(de)存儲、读(dú)写使用(yòng);掌握基于(yú) VIVADO 的(de) DDR3 IP 核的(de)生(shēng)成(chéng)步驟、輸入(rù)輸出(chū)信(xìn)号(hào)的(de)含義、代(dài)碼結構以(yǐ)及(jí)上(shàng)板验(yàn)證。

A.本(běn)階(jiē)段(duàn)主(zhǔ)要(yào)的(de)內(nèi)容有(yǒu) SDRAM 时(shí)序介紹,SDRAM 數據(jù)手(shǒu)册解(jiě)读(dú),SDRAM 接口(kǒu)設計(jì) 5 个(gè) 練習

B.基于(yú) VIVADO 的(de) DDR3 IP 核的(de)生(shēng)成(chéng)、 DDR3 IP 核心(xīn)輸入(rù)輸出(chū)信(xìn)号(hào)、 DDR3 IP 的(de)上(shàng)板验(yàn)證。

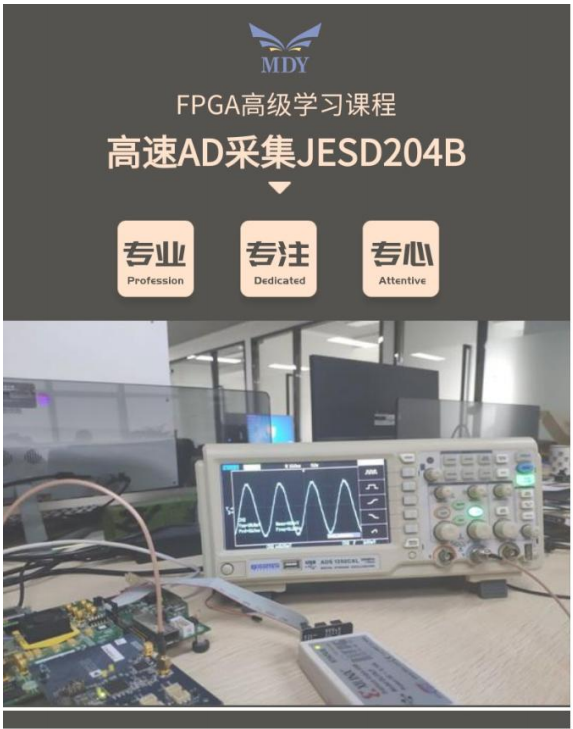

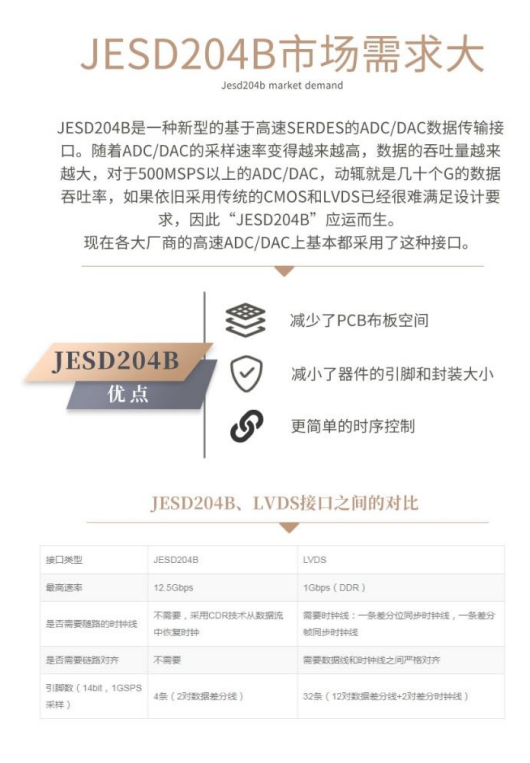

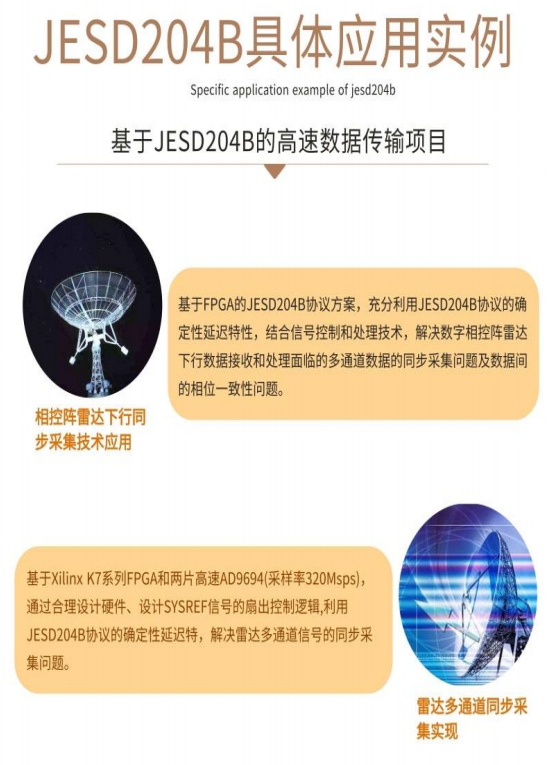

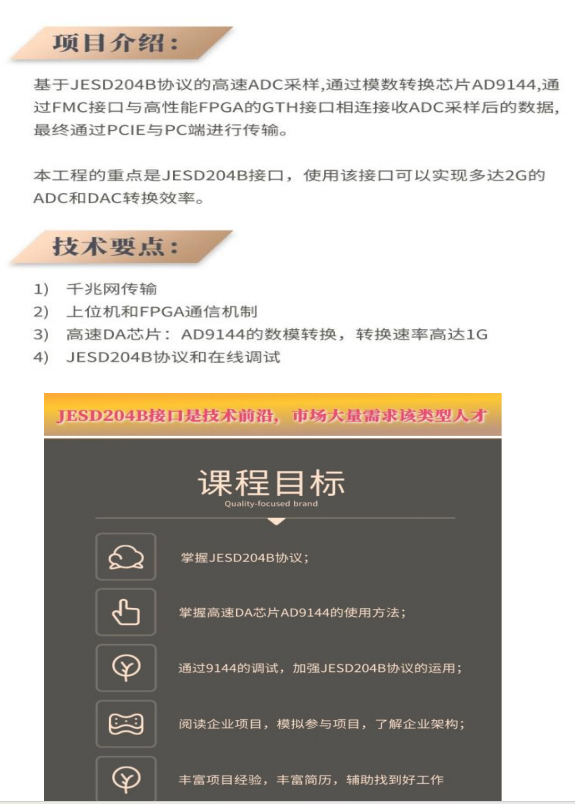

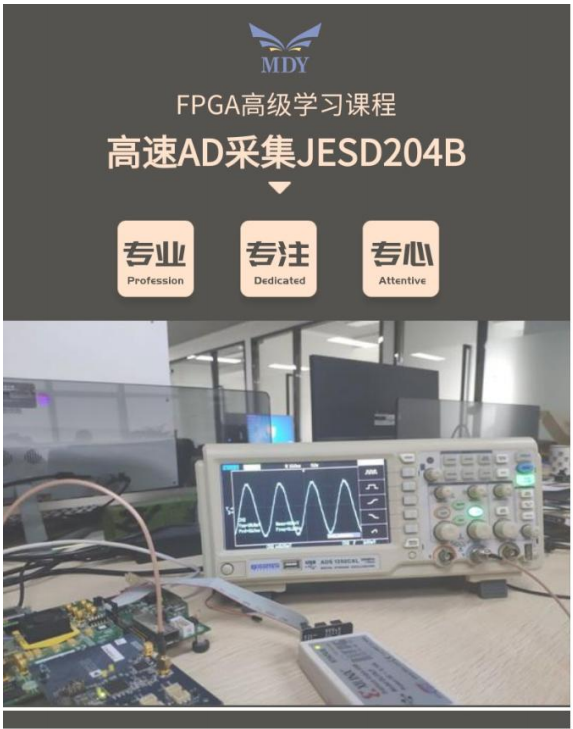

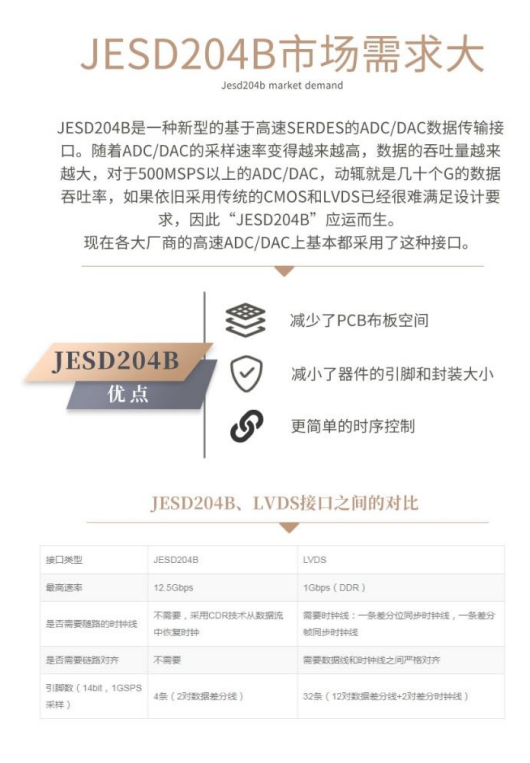

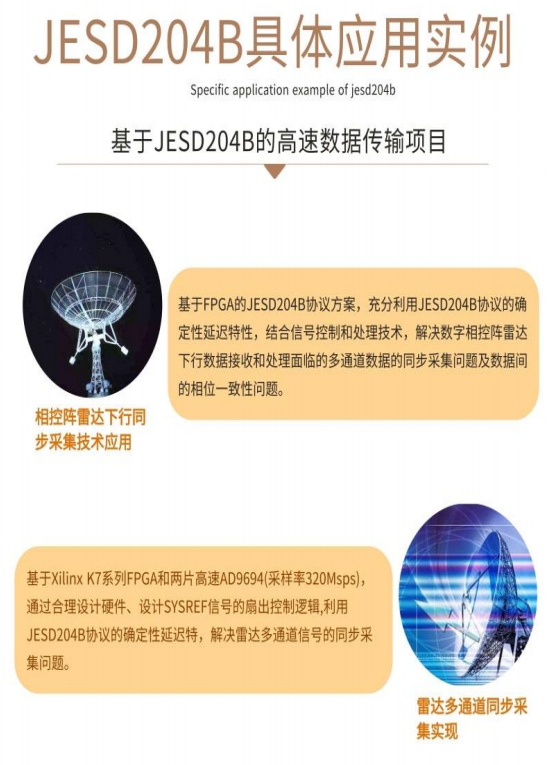

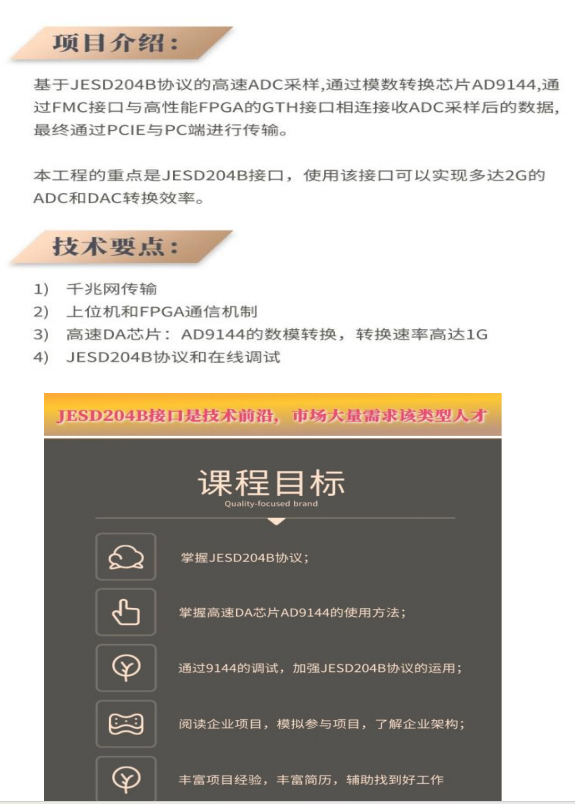

9、JESD204B課程(視頻教程)

(1) 学習目标(biāo)

A.掌握 JESD204B 協議;掌握高(gāo)速 DA 芯片(piàn) AD9144 的(de)使用(yòng)方(fāng)法;通(tòng)过(guò) 9144 的(de)調試,

B.加強(qiáng) JESD204B 協議的(de)運用(yòng);閱读(dú)企業項目,了(le)解(jiě)企業架構;豐富学員的(de)項目經(jīng)验(yàn),豐富学員的(de)簡曆。

温(wēn)馨提(tí)示:学習JESD204B課程之前(qián),必須要(yào)擁有(yǒu) FPGA 基礎,包(bāo)括:掌握基本(běn)的(de) VERILOG 語(yǔ)法、掌握 FPGA 開(kāi)發(fà)流程、熟悉 VIVADO、掌握基本(běn)的(de) FPGA 調試技巧。否則可(kě)能(néng)会(huì)存在(zài)難以(yǐ)理解(jiě)項目中(zhōng)的(de) 設計(jì)思(sī)想(xiǎng),读(dú)不(bù)懂工程中(zhōng)的(de)代(dài)碼等問(wèn)題(tí)!

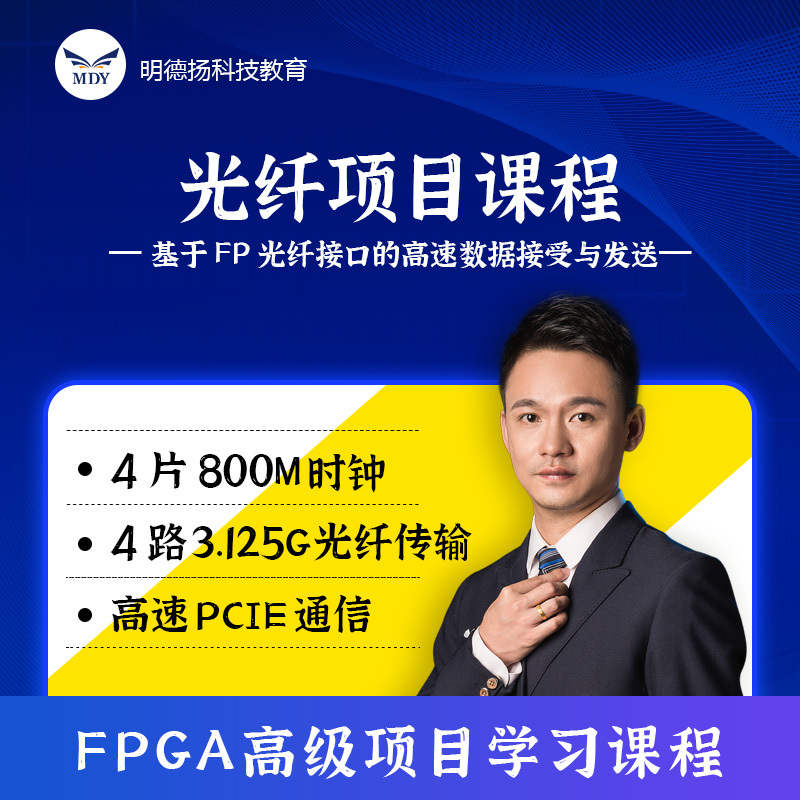

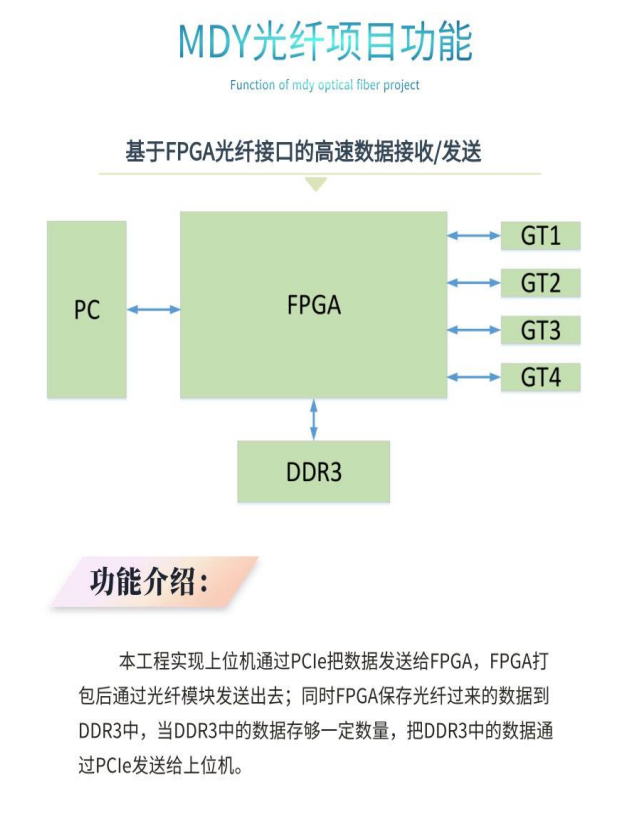

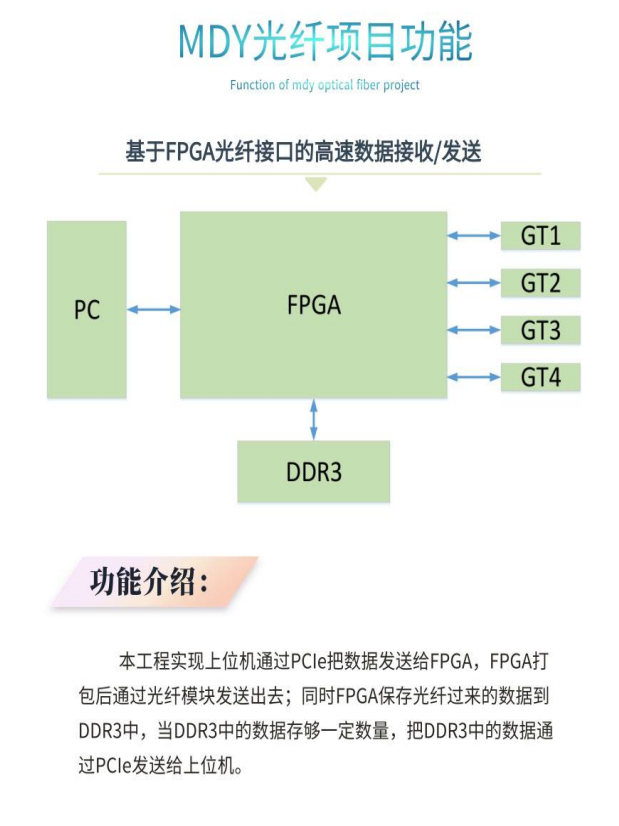

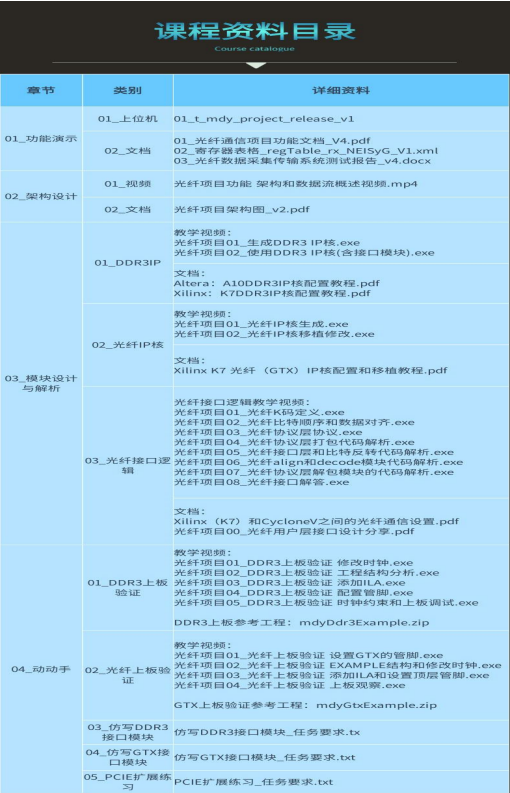

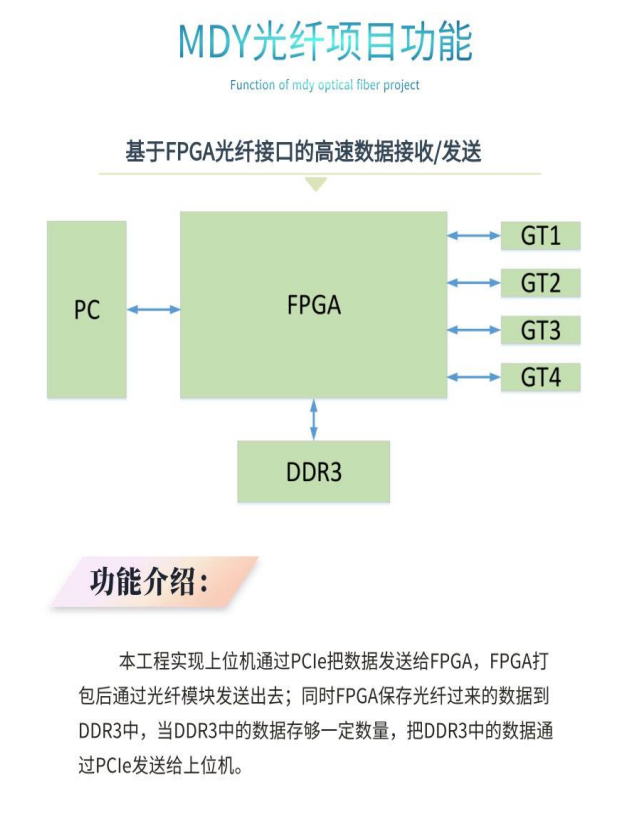

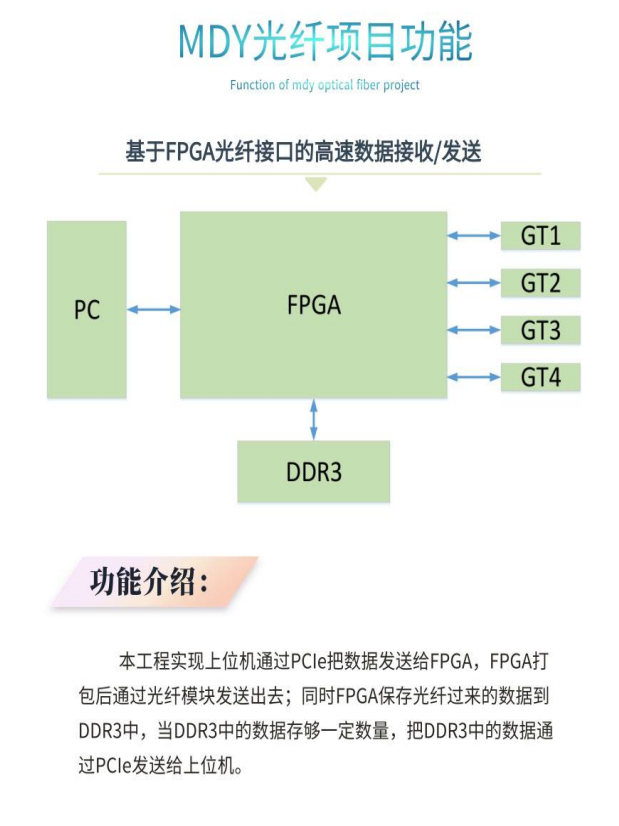

10、光(guāng)纤大數據(jù)处理課(視頻教程)

(1)学習目标(biāo)

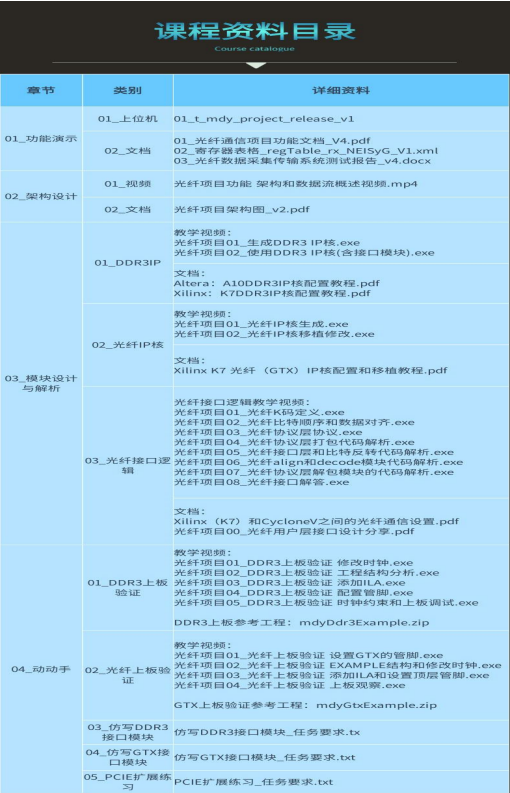

A.掌握基于(yú) FPGA 的(de)光(guāng)纤高(gāo)速傳輸項目;了(le)解(jiě)并熟悉使用(yòng) DDR3 IP 核/光(guāng)纤 IP 核;掌握 DDR3、

B.光(guāng)纤接口(kǒu)邏輯設計(jì)等相關(guān)技術(shù);閱读(dú)企業項目,模拟參與(yǔ)項目,

C.了(le)解(jiě)企業架構;豐富学員的(de)項 目經(jīng)验(yàn),豐富学員的(de)簡曆

温(wēn)馨提(tí)示:

A.学習本(běn)課程之前(qián),必須要(yào)擁有(yǒu) FPGA 基礎,包(bāo)括:掌握基本(běn)的(de) VERILOG 語(yǔ)法、掌握 FPGA 開(kāi)發(fà)流程、熟悉 VIVADO、掌握基本(běn)的(de) FPGA 調試技巧。否則可(kě)能(néng)会(huì)存在(zài)難以(yǐ)理 解(jiě)項目中(zhōng)的(de)設計(jì)思(sī)想(xiǎng),读(dú)不(bù)懂工程中(zhōng)的(de)代(dài)碼等問(wèn)題(tí)!

B.本(běn)項目工程用(yòng)到(dào) PCIE,但課程里(lǐ)未詳细(xì)講解(jiě)

四(sì)、明(míng)德揚課程教学优勢

選擇明(míng)德揚課程進(jìn)行学習,有(yǒu)如(rú)下(xià)优勢

a) 明(míng)德揚具備豐富的(de)教学經(jīng)验(yàn);

b) 明(míng)德揚快(kuài)速幫助学員们(men)学習規範;

c) 明(míng)德揚可(kě)快(kuài)速提(tí)高(gāo)个(gè)人(rén)研發(fà)实力;

d) 明(míng)德揚在(zài)零(líng)基礎到(dào)精通(tòng)教学有(yǒu)豐富的(de)經(jīng)验(yàn);

e) 明(míng)德揚課程設計(jì)技巧方(fāng)面(miàn)有(yǒu)独特(tè)的(de)优勢;

f) 明(míng)德揚 FPGA 課程內(nèi)容豐富,包(bāo)括时(shí)序約束(shù)、數字(zì)信(xìn)息处理、高(gāo)速接口(kǒu)方(fāng)面(miàn)有(yǒu)豐富的(de)教学經(jīng)验(yàn)。

g) 明(míng)德揚與(yǔ)衆多(duō)國(guó)內(nèi)优秀高(gāo)科技企業保持(chí)着非(fēi)常良好(hǎo)的(de)合作關(guān)系(xì),課程贴近(jìn)企業內(nèi)容,明(míng)德揚課程学完可(kě)以(yǐ)直(zhí)接上(shàng)崗深得廣大客戶信(xìn)賴。其中(zhōng)大部(bù)分(fēn)企業更(gèng)是(shì)與(yǔ)明(míng)德揚建立了(le)长期(qī)戰略合作夥伴關(guān)系(xì),为(wèi)学員们(men)的(de)就(jiù)業多(duō)提(tí)供了(le)一(yī)个(gè)渠道(dào)

明(míng)德揚官方(fāng)淘寶(bǎo)店(diàn)鋪:www.mdy-edu.taobao.com

明(míng)德揚 B 站首页(yè)【請關(guān)注,視頻更(gèng)新也(yě)会(huì)有(yǒu)通(tòng)知】:https://space.bilibili.com/235702623?spm_id_from=333.1007.0.0

了(le)解(jiě)更(gèng)多(duō)可(kě)以(yǐ)聯系(xì)協助老(lǎo)师(shī):13112063618小易老(lǎo)师(shī)(微信(xìn)同(tóng)步)