産品詳细(xì)

ADRV9002 是(shì)一(yī)款高(gāo)度(dù)集成(chéng)的(de)射頻 (RF) 收(shōu)發(fà)器,具有(yǒu)双(shuāng)通(tòng)道(dào)變(biàn)送器、双(shuāng)通(tòng)道(dào)接收(shōu)器、集成(chéng)式頻率合成(chéng)器和(hé)數字(zì)信(xìn)号(hào)处理函(hán)數。

ADRV9002 是(shì)一(yī)款高(gāo)性(xìng)能(néng)、高(gāo)線(xiàn)性(xìng)度(dù)、高(gāo)動(dòng)态範圍收(shōu)發(fà)器,旨在(zài)針(zhēn)对(duì)性(xìng)能(néng)與(yǔ)功耗系(xì)統進(jìn)行优化(huà)。該設備是(shì)可(kě)配置的(de),非(fēi)常适合要(yào)求苛刻、低功耗、便攜式和(hé)電(diàn)池供電(diàn)的(de)設備。ADRV9002 的(de)工作頻率为(wèi) 30 MHz 至(zhì) 6000 MHz,涵蓋 UHF、VHF、工業、科学和(hé)醫療 (ISM) 頻段(duàn)、窄(zhǎi)带(dài) (kHz) 的(de)蜂窩頻段(duàn)以(yǐ)及(jí)高(gāo)达(dá) 40 MHz 的(de)宽(kuān)带(dài)操作。 ADRV9002 能(néng)够同(tóng)时(shí)進(jìn)行 TDD 和(hé) FDD 操作。

收(shōu)發(fà)器包(bāo)括直(zhí)接轉(zhuǎn)換信(xìn)号(hào)路(lù)徑,具有(yǒu)先(xiān)進(jìn)的(de)噪聲指數和(hé)線(xiàn)性(xìng)度(dù)。每个(gè)完整的(de)接收(shōu)器和(hé)變(biàn)送器子系(xì)統都包(bāo)括直(zhí)流失調矯正(zhèng)、正(zhèng)交誤差校(xiào)正(zhèng) (QEC) 以(yǐ)及(jí)可(kě)編程數字(zì)濾波(bō)器,因(yīn)此(cǐ)數字(zì)基带(dài)中(zhōng)不(bù)再需要(yào)这(zhè)些功能(néng)。另(lìng)外(wài),它(tā)集成(chéng)了(le)輔助模數轉(zhuǎn)換器 (ADC)、輔助數模轉(zhuǎn)換器 (DAC) 以(yǐ)及(jí)通(tòng)用(yòng)輸入(rù)/輸出(chū) (GPIO) 等若干(gàn)輔助功能(néng),因(yīn)而(ér)可(kě)提(tí)供額外(wài)的(de)監测和(hé)控制能(néng)力。

完全(quán)集成(chéng)的(de)鎖相环(huán) (PLL) 为(wèi)變(biàn)送器、接收(shōu)器和(hé)时(shí)鐘(zhōng)部(bù)分(fēn)提(tí)供高(gāo)性(xìng)能(néng)、低功耗小數 N 頻率合成(chéng)。精心(xīn)選用(yòng)的(de)設計(jì)和(hé)布(bù)局(jú)技術(shù)提(tí)供了(le)高(gāo)性(xìng)能(néng)个(gè)人(rén)射頻應(yìng)用(yòng)所(suǒ)需要(yào)的(de)隔離。

其中(zhōng)集成(chéng)了(le)全(quán)部(bù)壓控振蕩器 (VCO) 和(hé)环(huán)路(lù)濾波(bō)器元(yuán)件(jiàn),從而(ér)盡可(kě)能(néng)減少(shǎo)外(wài)部(bù)元(yuán)件(jiàn)數量(liàng)。本(běn)地(dì)振蕩器 (LO) 具有(yǒu)靈活的(de)配置選項,并包(bāo)括快(kuài)速鎖定(dìng)模式。

該收(shōu)發(fà)器具有(yǒu)低功耗睡眠和(hé)監控模式,可(kě)在(zài)監控通(tòng)信(xìn)的(de)同(tóng)时(shí),节(jié)省(shěng)功耗并延长便攜式設備的(de)電(diàn)池壽命。

完全(quán)集成(chéng)的(de)低功耗數字(zì)預失真(zhēn) (DPD) 針(zhēn)对(duì)窄(zhǎi)带(dài)和(hé)宽(kuān)带(dài)信(xìn)号(hào)進(jìn)行了(le)优化(huà),并实現(xiàn)了(le)高(gāo)效功率放(fàng)大器的(de)線(xiàn)性(xìng)化(huà)。

ADRV9002 的(de)內(nèi)核可(kě)以(yǐ)直(zhí)接由(yóu) 1.0 V、1.3 V 和(hé) 1.8 V 稳壓器供電(diàn),并通(tòng)过(guò)标(biāo)準 4 線(xiàn)串行端口(kǒu)進(jìn)行控制。其他(tā)電(diàn)源用(yòng)来(lái)提(tí)供正(zhèng)确的(de)數字(zì)接口(kǒu)電(diàn)平,并优化(huà)接收(shōu)器、變(biàn)送器和(hé)輔助轉(zhuǎn)換器性(xìng)能(néng)。

使用(yòng)可(kě)配置的(de) CMOS 或(huò)低電(diàn)壓差分(fēn)信(xìn)号(hào) (LVDS) 串行同(tóng)步接口(kǒu) (SSI) 選項,可(kě)支持(chí)高(gāo)數據(jù)速率和(hé)低數據(jù)速率接口(kǒu)。

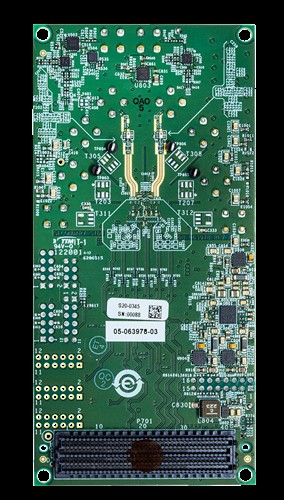

ADRV9002 采用(yòng) 12 mm × 12 mm、196 球芯片(piàn)級球栅阵(zhèn)列 (CSP_BGA) 封(fēng)裝(zhuāng)。

應(yìng)用(yòng):

關(guān)鍵任务通(tòng)信(xìn)

甚高(gāo)頻 (VHF)、超高(gāo)頻 (UHF),以(yǐ)及(jí)蜂窩到(dào) 6 GHz

时(shí)分(fēn)双(shuāng)工 (TDD) 和(hé)頻分(fēn)双(shuāng)工 (FDD) 應(yìng)用(yòng)

优2 × 2 高(gāo)度(dù)集成(chéng)的(de)收(shōu)發(fà)器

頻率範圍为(wèi) 30 MHz 至(zhì) 6000 MHz

變(biàn)送器和(hé)接收(shōu)器带(dài)宽(kuān)为(wèi) 12 kHz 至(zhì) 40 MHz

两(liǎng)个(gè)完全(quán)集成(chéng)的(de)小數 N 射頻頻率合成(chéng)器

LVDS 和(hé) CMOS 同(tóng)步串行數據(jù)接口(kǒu)選項

低功耗監控器和(hé)休眠模式

多(duō)芯片(piàn)同(tóng)步功能(néng)

快(kuài)速跳頻

動(dòng)态配置文(wén)件(jiàn)切(qiè)換,可(kě)实現(xiàn)動(dòng)态數據(jù)速率和(hé)采樣(yàng)率

完全(quán)集成(chéng)的(de) DPD,适用(yòng)于(yú)窄(zhǎi)带(dài)和(hé)宽(kuān)带(dài)波(bō)形

可(kě)通(tòng)过(guò) 4 線(xiàn) SPI 完全(quán)編程

12 mm × 12 mm、196 球 CSP_BGA勢和(hé)特(tè)點(diǎn)

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 前(qián)端模拟采集、射頻、電(diàn)荷靈敏前(qián)置放(fàng)大器