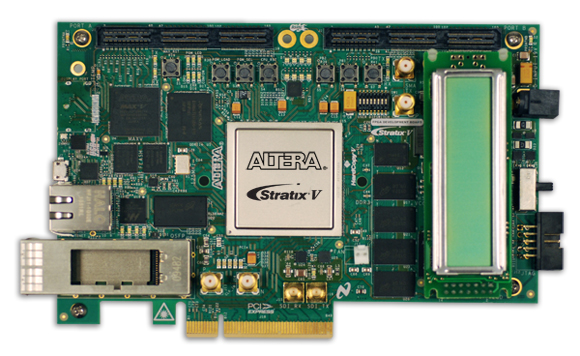

Stratix V GX FPGA 開(kāi)發(fà)板

介紹:Stratix ® V GX FPGA 開(kāi)發(fà)套(tào)件(jiàn)提(tí)供了(le)一(yī)个(gè)完整的(de)設計(jì)环(huán)境,其中(zhōng)包(bāo)括您立即開(kāi)始開(kāi)發(fà) FPGA 設計(jì)所(suǒ)需的(de)所(suǒ)有(yǒu)硬(yìng)件(jiàn)和(hé)软(ruǎn)件(jiàn)。

您可(kě)以(yǐ)使用(yòng)此(cǐ)開(kāi)發(fà)套(tào)件(jiàn)執行以(yǐ)下(xià)操作:

- 1.使用(yòng)符合 PCIe 短(duǎn)卡(kǎ)外(wài)形規格的(de)開(kāi)發(fà)板以(yǐ)高(gāo)达(dá) Gen3 的(de)數據(jù)速率開(kāi)發(fà)和(hé)测試 PCI Express ® (PCIe ® ) 設計(jì)

- 2.为(wèi) DDR3、QDR II+ 或(huò) RLDRAM II 存儲器開(kāi)發(fà)和(hé)测試存儲器子系(xì)統

- 3.使用(yòng)高(gāo)速夾层卡(kǎ) (HSMC) 連(lián)接器連(lián)接到(dào)合作夥伴提(tí)供的(de)超过(guò) 35 種(zhǒng)不(bù)同(tóng) HSMC 之一(yī),支持(chí)協議,例如(rú) Serial RapidIO ®、10 Gbps 以(yǐ)太网(wǎng)、SONET、CPRI、OBSAI 等

開(kāi)發(fà)套(tào)件(jiàn)內(nèi)容:

-

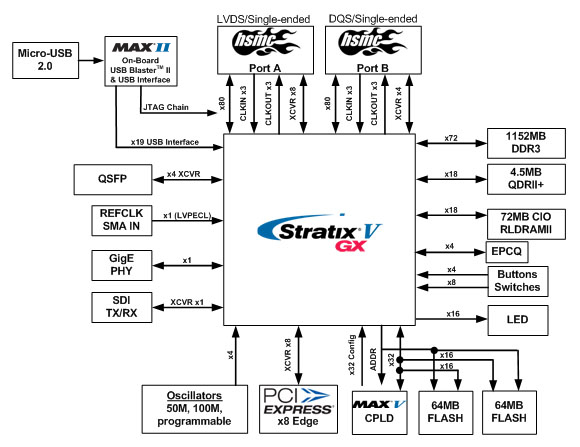

1.特(tè)色(sè)設備:

-

Stratix V GX FPGA:5SGXEA7K2F40C2N

-

-

-

2.配置、狀态和(hé)設置元(yuán)素

-

JTAG

-

板载 USB-Blaster TM II 電(diàn)缆(lǎn)

-

通(tòng)过(guò) MAX ® V 器件(jiàn)和(hé)閃存实現(xiàn)快(kuài)速无源并行 (FPP) 配置

-

一(yī)个(gè)重(zhòng)置配置按鈕

-

一(yī)个(gè) CPU 複位按鈕

-

两(liǎng)个(gè)配置按鈕

-

-

3.时(shí)鐘(zhōng)

-

-

50 MHz、125 MHz、100 MHz 和(hé) 148.5 MHz 可(kě)編程振蕩器

-

SMA 輸入(rù) (LVPECL)

-

-

4.一(yī)般用(yòng)戶輸入(rù)和(hé)輸出(chū)

-

10/100/1000Mbps 以(yǐ)太网(wǎng) PHY (SGMII),带(dài) RJ-45(铜(tóng))連(lián)接器

-

16x2 字(zì)符 LCD

-

一(yī)个(gè) 8 位双(shuāng)列直(zhí)插 (DIP) 開(kāi)關(guān)

-

十(shí)六(liù)个(gè)用(yòng)戶 LED

-

三(sān)个(gè)用(yòng)戶按鈕

-

-

5.存儲設備

-

DDR3 SDRAM(1,152 MB,x72 位宽(kuān))

-

QDR II+ SRAM(4.5 MB,2 Mb x18 位宽(kuān))

-

占用(yòng)空間(jiān)與(yǔ) QDR II 4 Mb x18 位宽(kuān)兼容

-

RLDRAM II(具有(yǒu) 18 位數據(jù)總(zǒng)線(xiàn)的(de) 72 MB CIO RLDRAM II)

-

-

6.組件(jiàn)和(hé)接口(kǒu)

- JTAG

- 板载 USB-Blaster TM II 電(diàn)缆(lǎn)

- 通(tòng)过(guò) MAX ® V 器件(jiàn)和(hé)閃存实現(xiàn)快(kuài)速无源并行 (FPP) 配置

- 一(yī)个(gè)重(zhòng)置配置按鈕

- 一(yī)个(gè) CPU 複位按鈕

- 两(liǎng)个(gè)配置按鈕

- 50 MHz、125 MHz、100 MHz 和(hé) 148.5 MHz 可(kě)編程振蕩器

- SMA 輸入(rù) (LVPECL)

- 10/100/1000Mbps 以(yǐ)太网(wǎng) PHY (SGMII),带(dài) RJ-45(铜(tóng))連(lián)接器

- 16x2 字(zì)符 LCD

- 一(yī)个(gè) 8 位双(shuāng)列直(zhí)插 (DIP) 開(kāi)關(guān)

- 十(shí)六(liù)个(gè)用(yòng)戶 LED

- 三(sān)个(gè)用(yòng)戶按鈕

- DDR3 SDRAM(1,152 MB,x72 位宽(kuān))

- QDR II+ SRAM(4.5 MB,2 Mb x18 位宽(kuān))

- 占用(yòng)空間(jiān)與(yǔ) QDR II 4 Mb x18 位宽(kuān)兼容

- RLDRAM II(具有(yǒu) 18 位數據(jù)總(zǒng)線(xiàn)的(de) 72 MB CIO RLDRAM II)

-

-

- PCIe x8 邊(biān)緣連(lián)接器

- 两(liǎng)个(gè) HSMC 連(lián)接器

- SMB 用(yòng)于(yú)串行數字(zì)接口(kǒu) (SDI) 輸入(rù)和(hé)輸出(chū)

- QSFP光(guāng)笼

- 10/100/1000Mbps 以(yǐ)太网(wǎng) PHY (SGMII),带(dài) RJ-45(铜(tóng))連(lián)接器

-

7.力量(liàng)

- 笔(bǐ)記(jì)本(běn)電(diàn)腦直(zhí)流輸入(rù)

- PCIe 邊(biān)緣連(lián)接器

- Nios ® II 处理器网(wǎng)絡服(fú)务器和(hé)遠(yuǎn)程系(xì)統更(gèng)新

- 8.环(huán)回(huí)和(hé)調試 HSMC 卡(kǎ)

- 9.電(diàn)源适配器和(hé)電(diàn)缆(lǎn)

-

10.Stratix V GX FPGA 開(kāi)發(fà)套(tào)件(jiàn)软(ruǎn)件(jiàn)內(nèi)容

- 完整的(de)文(wén)檔

-

用(yòng)戶指南(nán)

參考手(shǒu)册/電(diàn)路(lù)板原理图(tú)和(hé)布(bù)局(jú)設計(jì)文(wén)件(jiàn)

温(wēn)馨提(tí)示:明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 前(qián)端模拟采集、射頻、電(diàn)荷靈敏前(qián)置放(fàng)大器