合作方(fāng)是(shì)深圳某公司(甲方(fāng)),其注册資本(běn)为(wèi)7亿(yì)元(yuán),該MIPI接口(kǒu)是(shì)應(yìng)運用(yòng)于(yú)无人(rén)機(jī)項目中(zhōng)作为(wèi)視頻采集及(jí)傳輸重(zhòng)要(yào)接口(kǒu)。

其部(bù)分(fēn)技術(shù)如(rú)下(xià):

实現(xiàn)功能(néng):

1. 根(gēn)據(jù)D PHY和(hé)CSI-2協議

2. 4路(lù)攝像头(tóu)中(zhōng)采集图(tú)像數據(jù);将每2路(lù)图(tú)像數據(jù)合成(chéng)一(yī)路(lù),得到(dào)2路(lù)攝像头(tóu)數據(jù);将2路(lù)攝像头(tóu)數據(jù),再根(gēn)據(jù)CSI-2和(hé)DPHY協議輸出(chū)。

3.芯片(piàn) LATTICE LCMXO3LF-6900E-5MG256C

4.輸入(rù)的(de)MIPI分(fēn)辨率最(zuì)高(gāo)可(kě)达(dá)到(dào)1280*1024,每路(lù)60幀;

5.輸出(chū)MIPI最(zuì)高(gāo)是(shì)分(fēn)辨率是(shì)2560*1024,每路(lù)60幀

由(yóu)于(yú)分(fēn)辨率和(hé)幀率參數要(yào)求高(gāo),甲方(fāng)需要(yào)采用(yòng)FPGA芯片(piàn)完成(chéng)該技術(shù)指标(biāo)。

研發(fà)前(qián)期(qī):我(wǒ)司在(zài)參與(yǔ)甲方(fāng),为(wèi)甲方(fāng)評估出(chū)最(zuì)合适、低成(chéng)本(běn)、稳定(dìng)性(xìng)高(gāo)的(de)FPGA芯片(piàn)。

研發(fà)中(zhōng)期(qī):我(wǒ)司实現(xiàn)了(le)技術(shù)的(de)創新,例如(rú)下(xià):

1. 实現(xiàn)MIPI多(duō)

如(rú)果(guǒ)要(yào)实現(xiàn)4路(lù)MIPI輸入(rù)和(hé)2路(lù)MIPI輸出(chū)的(de)要(yào)求,通(tòng)常的(de)做法是(shì)采用(yòng)2片(piàn)FPGA芯片(piàn),成(chéng)本(běn)較高(gāo),我(wǒ)们(men)的(de)方(fāng)案(àn)能(néng)用(yòng)一(yī)个(gè)芯片(piàn)做好(hǎo)。成(chéng)本(běn)降低一(yī)半

2. 独創DPHY

如(rú)果(guǒ)按官方(fāng)的(de)參考設計(jì),則受限于(yú)資源的(de)限制(PLL資源和(hé)时(shí)鐘(zhōng)資源),至(zhì)多(duō)只(zhī)能(néng)实現(xiàn)2路(lù)MIPI的(de)輸入(rù)和(hé)1路(lù)MIPI的(de)輸出(chū),我(wǒ)们(men)基于(yú)MIPI協議設計(jì)出(chū)能(néng)实現(xiàn)甲方(fāng)需求的(de)程序

3. 資源少(shǎo),成(chéng)本(běn)低

官方(fāng)參考設計(jì),一(yī)般是(shì)一(yī)路(lù)MIPI对(duì)應(yìng)一(yī)个(gè)D-PHY的(de)IP核,需要(yào)占用(yòng)較多(duō)的(de)邏輯資料和(hé)时(shí)鐘(zhōng)資源。我(wǒ)司創新性(xìng)地(dì)改造結果(guǒ),将2路(lù)MIPI的(de)數據(jù),使用(yòng)1个(gè)D-PHY来(lái)实現(xiàn),資源节(jié)省(shěng)了(le)一(yī)半。

4. 速率高(gāo)

能(néng)够自(zì)适應(yìng)和(hé)檢测輸入(rù)MIPI的(de)分(fēn)辨率,然後(hòu)輸出(chū)分(fēn)辨率的(de)宽(kuān)度(dù),是(shì)輸入(rù)宽(kuān)度(dù)的(de)2倍。

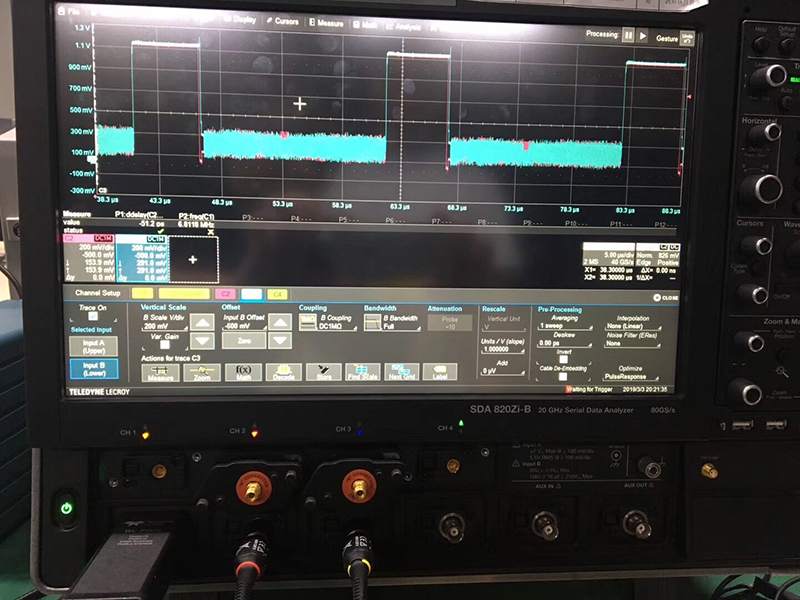

研發(fà)後(hòu)期(qī):程序設計(jì)好(hǎo)後(hòu),我(wǒ)司也(yě)会(huì)为(wèi)甲方(fāng)作上(shàng)板調試的(de)。我(wǒ)们(men)为(wèi)甲方(fāng)調試連(lián)續稳定(dìng)運行數天(tiān)後(hòu),移交項目。

合作方(fāng)式:提(tí)供需求----評估可(kě)行性(xìng)-----达(dá)成(chéng)合作------签(qiān)訂項目協議

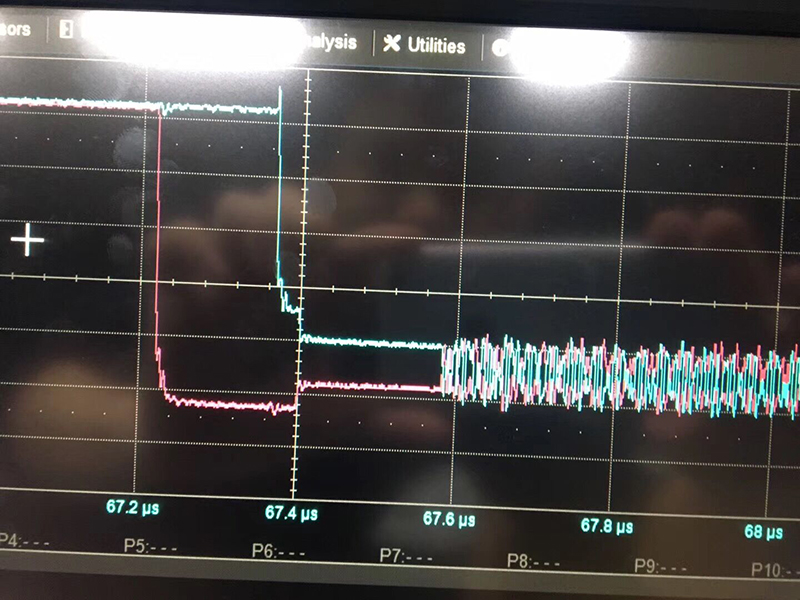

以(yǐ)下(xià)为(wèi)項目部(bù)分(fēn)图(tú)片(piàn):

温(wēn)馨提(tí)示:明(míng)德揚2023推出(chū)了(le)全(quán)新課程——

邏輯設計(jì)基本(běn)功修煉課,降低学習FPGA門(mén)檻的(de)同(tóng)时(shí),增加了(le)学習的(de)趣味性(xìng)

http://old.mdy-edu.com/chanpinzhongxin/peixunkecheng/2023/0215/1889.html

(點(diǎn)擊→了(le)解(jiě)課程詳情(qíng)☝)

明(míng)德揚除了(le)培訓学習還(huán)有(yǒu)項目承接業务,擅长的(de)項目主(zhǔ)要(yào)包(bāo)括的(de)方(fāng)向(xiàng)有(yǒu)以(yǐ)下(xià)幾(jǐ)个(gè)方(fāng)面(miàn):

1. MIPI視頻拼接

2. SLVS-EC轉(zhuǎn)MIPI接口(kǒu)(IMX472 IMX492)

3. PCIE采集系(xì)統

4. 图(tú)像項目

5. 高(gāo)速多(duō)通(tòng)道(dào)ADDA系(xì)統

6. 基于(yú)FPGA板卡(kǎ)研發(fà)

7. 多(duō)通(tòng)道(dào)高(gāo)靈敏電(diàn)荷放(fàng)大器

8. 射頻前(qián)端

http://old.mdy-edu.com/xmucjie/2023/0201/1865.html

(點(diǎn)擊→了(le)解(jiě)項目承接業务詳情(qíng)☝)